### João Alexandre Abreu Ferreira

# Real-time implementation of combined Ring-type Magnitude Modulation and LINC techniques on SoC Zynq-7000 Architecture

Dissertação submetida para obtenção do grau de Mestre em Engenharia Eletrotécnica e de Computadores, Área de Especialização em Telecomunicações

Setembro de 2015

Universidade de Coimbra

### Real-time implementation of combined Ring-Type Magnitude Modulation and LINC techniques on SoC Zynq-7000 Architecture

João Alexandre Abreu Ferreira

Dissertação para obtenção do Grau de Mestre em **Engenharia Eletrotécnica e de Computadores**

Orientador:Doutor Marco Alexandre Cravo GomesCo-Orientador:Doutor Vítor Manuel Mendes da Silva

### Júri

Presidente:Doutora Maria do Carmo Raposo de MedeirosOrientador:Doutor Marco Alexandre Cravo GomesVogais:Doutor Mário João Simões Ferreira dos Santos

Setembro de 2015

## Agradecimentos

Chegou ao fim mais uma etapa da minha vida. Este trabalho é precisamente o culminar desta viagem que agora dá lugar a outra, a da vida profissional. Com isto, não posso deixar de agradecer à minha família mais próxima, em especial aos meus pais é à "mana", que estiveram sempre ao meu lado e me apoiaram ao longo desta jornada.

Agradeço também aos meus amigos e colegas de curso, que me acompanharam na vida de estudante, quer tenha sido para a praxe, jantares, grandes maratonas de estudo ou simples procissões à máquina do café, para 15 minutos de conversa.

Aos professores Marco Gomes e Vítor Silva, pelo tempo que me dedicaram ao longo deste trabalho, especialmente quando parecia não haver soluções à vista, e também a todos os professores do DEEC, pela dedicação e entrega que mostram todos os dias ao leccionar este curso. Também à professora Natália Reis, pela ajuda que me deu para melhorar a escrita em Inglês em todo este trabalho.

Aos meus colegas de laboratório, que estiveram sempre disponíveis para ajudar.

A todos, Muito Obrigado.

## Abstract

The development of low-cost systems is a constant goal of Telecommunications engineering, where bandwidth and transmitting power are resources that need to be optimized, especially in mobile devices. In these cases, in which it is necessary to use power amplification (PA) for radio-frequencies (RF), power efficiency becomes one of the main focuses. In most cases, amplification is achieved through high power amplifiers (HPA) with a high level of linearity, which is a requirement in case the signals to transmit have high peak-to-average-power ratio (PAPR), which is typical in signals with high spectral efficiency. One way to avoid this problem is to use the Linear Amplification with Nonlinear Components (LINC) technique. However, digital LINC implementation has large oversampling requirements, as well as its power efficiency gains are limited at the LINC's combiner stage by the PAPR of the signals to transmit.

In the project GLANCES (UID/EEA/50008/2013) from the Instituto de Telecomunicações, a new transmitter front-end architecture was envisioned. Leveraging on the decomposition of high order constellations as a sum of offset-quadrature phase sift keying (OQPSK) signals, is it possible to use LINC techniques on the separate amplification of each OQPSK component, with considerable gains in efficiency due to the much lower OQPSK signal's PAPR. This performance can even be leverage by a new proposed Ring-Magnitude Modulation (RMM) technique, that warranties a perfect amplitude ring shape of a bandwidth limited OQPSK signal at the input of the LINC amplifier.

This thesis aims to develop a proof of concept of the described system, working in real time and supported by a field programmable gate array (FPGA) architecture: Zynq-7000 system on chip (SoC), to implement LINC techniques together with ring-type magnitude modulation (RMM), with two different *hardware* approaches: 1) a look-up table (LUT) based implementation for each of the LINC and RMM techniques and 2) a LUT based implementation for RMM and a hardware module to perform the LINC decomposition, based in its vectorial form.

## Keywords

LINC, RMM, OQPSK, FPGA, SoC, LUT, Real Time, Signal Processing

## Resumo

O desenvolvimento de sistemas de baixo custo é um marco constante na ciência das Telecomunicações, onde a largura de banda e a energia dispendida para transmissão são meios escassos que precisam de ser otimizados, principalmente em dispositivos móveis. Nestes casos, em que é necessário recorrer a amplificação de potência para radio-frequências (RF), a eficiência energética torna-se num dos principais focos de atenção. Na maioria dos casos, a amplificação é conseguida através de amplificadores de alta potência (HPA) com elevada linearidade, linearidade essa que é um requisito importante caso o sinal a transmitir tenha uma elevada relação entre a potência de pico e a poteência média (PAPR), o que é habitual em sinais com alta eficiência espectral. Uma das respostas a este problema é uma técnica chamada Amplificação Linear através de Componentes Não-Lineares (LINC). No entanto, a implementação digital LINC tem requisitos elevados de sobreamostragem, e os seus ganhos de potência são limitados no combinador LINC pelo PAPR dos sinais a transmitir. No projeto GLANCES (UID/EEA/50008/2013) do Instituto de Telecomunicações, uma nova arquitectura de transmissores foi desenvolvida. Baseandose no facto de constelações de maior ordem poderem ser decompostas numa soma de sinais com modulação digital de fase em quadratura OQPSK, mostra-se ser possível usar técnicas LINC na amplificação de cada uma das componentes OQPSK, com ganhos consideráveis que se devem ao PAPR muito mais baixo apresentado por estas constelações. Este desempenho pode ainda ser melhorado por uma técnica inovadora: Modulação de Mangitude em Anel (RMM), que garante a forma anelar da amplitude de um sinal OQPSK de banda limitada à entrada do amplificador LINC. Este projeto de tese pretende desenvolver uma prova de conceito de um sistema de tempo real, suportado por uma arquitetura FPGA Zynq-7000 SoC para implementação conjunta de decomposição LINC e de RMM, com duas aproximações diferentes ao problema, feitas em hardware: 1) um sistema baseado em tabelas de consulta (LUT) para cada uma das técnicas LINC e RMM e 2) um sistema baseado em LUT para a implementação da RMM e um módulo de cálculo em hardware para a decomposição LINC, na sua forma vetorial.

## **Palavras Chave**

LINC, RMM, OQPSK, FPGA, SoC, LUT, Tempo Real, Processamento de Sinal

# Contents

| 1 | Introduction 1 |                                                         |  |  |  |  |

|---|----------------|---------------------------------------------------------|--|--|--|--|

|   | 1.1            | Objectives                                              |  |  |  |  |

|   | 1.2            | Dissertation Outline                                    |  |  |  |  |

|   | 1.3            | Thesis framework and contributions    6                 |  |  |  |  |

| 2 | LIN            | C systems 7                                             |  |  |  |  |

|   | 2.1            | Basic concepts for LINC systems                         |  |  |  |  |

|   |                | 2.1.1 Angle decomposition                               |  |  |  |  |

|   |                | 2.1.2 Vector decomposition                              |  |  |  |  |

|   |                | 2.1.3 LINC branches matching                            |  |  |  |  |

|   | 2.2            | Digital LINC transmission system                        |  |  |  |  |

|   |                | 2.2.1 Parameter-imposed limits                          |  |  |  |  |

| 3 | Mag            | itude Modulation 15                                     |  |  |  |  |

|   | 3.1            | The Magnitude Modulation Principle    16                |  |  |  |  |

|   |                | 3.1.1 Look-Up Table Based Approach                      |  |  |  |  |

|   | 3.2            | Ring-type Magnitude Modulation applied to OQPSK signals |  |  |  |  |

|   |                | 3.2.1 LUT scheme                                        |  |  |  |  |

|   |                | 3.2.2 Table size and parameters                         |  |  |  |  |

|   |                | 3.2.3 Symbol storage and search                         |  |  |  |  |

|   |                | 3.2.4 Final acknowledgments                             |  |  |  |  |

| 4 | Arc            | itecture Design 23                                      |  |  |  |  |

|   | 4.1            | Hardware and Workspace                                  |  |  |  |  |

|   |                | 4.1.1 ZC702                                             |  |  |  |  |

|   |                | 4.1.2 FMC30RF                                           |  |  |  |  |

|   |                | 4.1.3 Other equipment                                   |  |  |  |  |

|   | 4.2            | System Architecture and Implementations                 |  |  |  |  |

|   |                | 4.2.1 Project backbone - Stellar IP                     |  |  |  |  |

|   |                | 4.2.2 RRC filter - Core Generator                       |  |  |  |  |

|   |     | 4.2.3    | LINC and RMM - Vivado HLS                     | 34 |

|---|-----|----------|-----------------------------------------------|----|

|   |     | 4.2.4    | Complete project - Xilinx ISE                 | 39 |

|   |     | 4.2.5    | Board programming - Xilinx SDK                | 43 |

|   |     | 4.2.6    | Board communication - Microsoft Visual Studio | 44 |

|   |     | 4.2.7    | External acquirements - GNU-Radio             | 45 |

| 5 | Imp | lementa  | tion and Simulation                           | 47 |

|   | 5.1 | ZC702    | total resources' capacity                     | 48 |

|   | 5.2 | Blocks   | ' specifications and physical occupation      | 48 |

|   |     | 5.2.1    | Generator with RMM and upscaling              | 49 |

|   |     |          | 5.2.1.A Timing and resources                  | 51 |

|   |     |          | 5.2.1.B Bit rate                              | 51 |

|   |     | 5.2.2    | Root-Raised Cosine Filter                     | 52 |

|   |     |          | 5.2.2.A Timing and resources                  | 52 |

|   |     |          | 5.2.2.B Bit rate                              | 54 |

|   |     | 5.2.3    | LINC decomposer                               | 54 |

|   |     |          | 5.2.3.A Timing and resources                  | 54 |

|   |     |          | 5.2.3.B Bit rate                              | 55 |

|   | 5.3 | Compl    | ete system                                    | 56 |

|   |     | 5.3.1    | Original system' occupation                   | 56 |

|   |     | 5.3.2    | System #1's occupation and results            | 57 |

|   |     | 5.3.3    | System #2's occupation and results            | 58 |

|   | 5.4 | Final c  | comparison and observations                   | 59 |

| 6 | Con | clusions | 3                                             | 61 |

|   | 6.1 | Future   | work                                          | 62 |

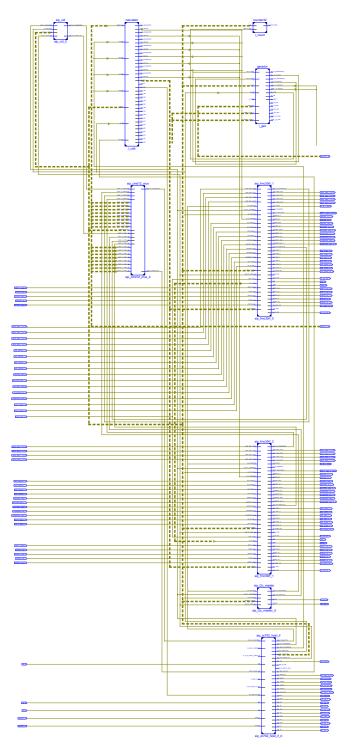

| A | Imp | lemente  | ed ISE VHDL schematic                         | 67 |

| D | FID | Filton I | mplementation                                 | 69 |

| D | ΓIN | ritter 1 | inprementation                                | 09 |

| С | LIN | C Look   | -Up Table                                     | 73 |

| D | C++ | Code o   | f the Implemented Blocks in HLS               | 75 |

|   |     |          | Calculator                                    | 76 |

|   | D.2 | LUT L    | INC                                           | 77 |

|   | D.3 | Genera   | ator                                          | 78 |

| Е | VHDL Code of the Implemented Snippets in ISE |                         |    |

|---|----------------------------------------------|-------------------------|----|

|   | E.1                                          | Counter                 | 82 |

|   | E.2                                          | RMM activator           | 83 |

|   | E.3                                          | Output channel selector | 83 |

Contents

# **List of Figures**

| 2.1  | LINC decomposition technique using two different representations 8       |    |

|------|--------------------------------------------------------------------------|----|

| 2.2  | Basic digital LINC transmission system.                                  | 12 |

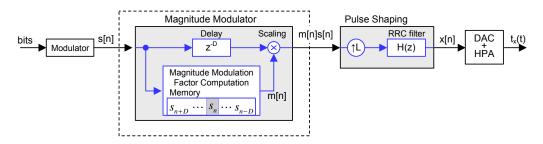

| 3.1  | Generic SC transmitter scheme.                                           | 16 |

| 3.2  | Magnitude modulation principle                                           | 16 |

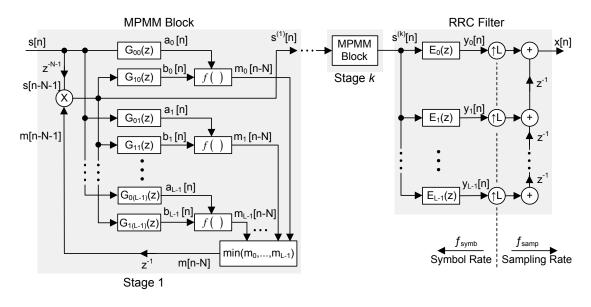

| 3.3  | MPMM principle                                                           | 17 |

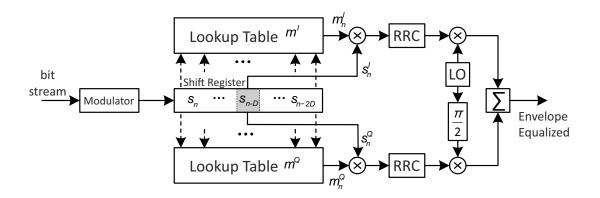

| 3.4  | Generic LUT-based Ring-type Magnitude Modulation transmitter scheme      |    |

|      | [1]                                                                      | 18 |

| 3.5  | Considered buffer scheme                                                 | 21 |

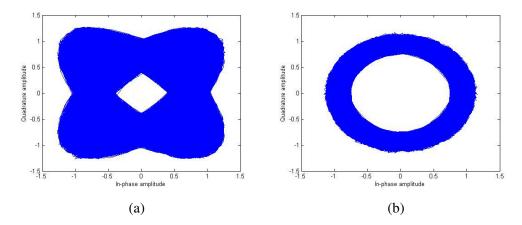

| 3.6  | Diagrams of the transition path between the constellation's symbols of a |    |

|      | ring-type magnitude modulated OQPSK signal without RMM (3.6a) and        |    |

|      | with RMM (3.6b)                                                          | 21 |

| 4.1  | Chosen boards.                                                           | 25 |

| 4.2  | High Level Block Diagram of Zynq-7000 XC7Z020 AP SoC                     | 26 |

| 4.3  | High Level Block Diagram of FMC30RF.                                     | 26 |

| 4.4  | FMC30RF supplied firmware schematic.                                     | 27 |

| 4.5  | Complete diagram of the hardware setup                                   | 28 |

| 4.6  | System flow                                                              | 29 |

| 4.7  | Complete software schematic.                                             | 29 |

| 4.8  | Stellar IP workspace                                                     | 30 |

| 4.9  | Generated Stellar IP design.                                             | 32 |

| 4.10 | Vivado HLS workspace.                                                    | 34 |

| 4.11 | Vivado HLS main action buttons                                           | 35 |

| 4.12 | Generator block diagram.                                                 | 36 |

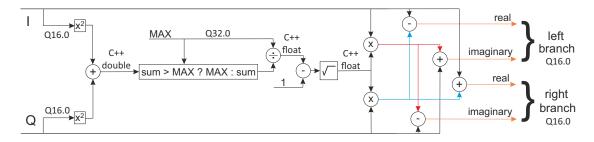

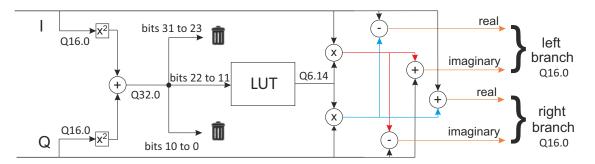

| 4.13 | LINC calculator block diagram.                                           | 37 |

| 4.14 | LUT LINC block diagram.                                                  | 38 |

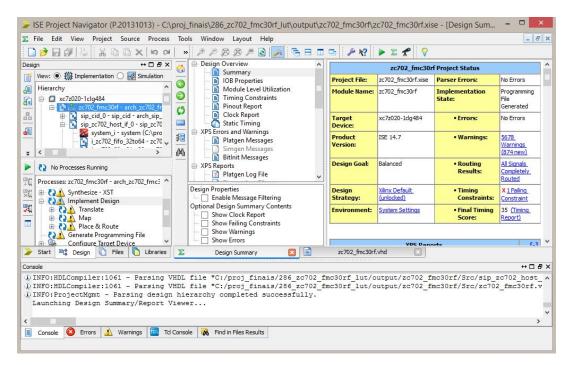

| 4.15 | Xilinx ISE workspace.                                                    | 39 |

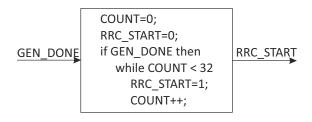

| 4.16 | Graphic implementation of the Counter block                              | 40 |

| 4.17 | Implemented code for left button.                                        | 41 |

| 4.18        | Implemented code for right button                            | 41 |

|-------------|--------------------------------------------------------------|----|

| 4.19        | ZC702's assigned buttons for the above mentioned code blocks | 42 |

| 4.20        | Block-diagram of the implemented parts of the project        | 42 |

| 4.21        | Xilinx SDK environment                                       | 43 |

| 4.22        | Microsoft Visual Studio environment.                         | 45 |

| 4.23        | GNU-Radio project                                            | 46 |

| 5.1         | Histogram of RNG.                                            | 50 |

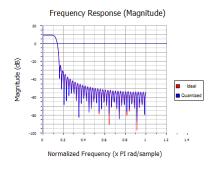

| 5.2         | Comparison of filters #1 and #2 for the same random sequence | 53 |

| 5.3         | Output of RRC filter - LUT implementation                    | 57 |

| 5.4         | Output of LINC left branch - LUT implementation              | 58 |

| 5.5         | Output of RRC filter - Calculator implementation             | 59 |

| 5.6         | Output of LINC left arm - Calculator implementation          | 59 |

| A.1         | Complete VHDL design, translated to RTL                      | 68 |

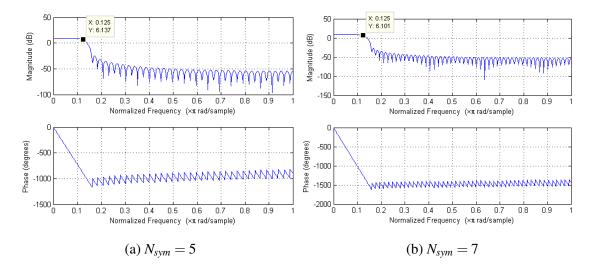

| <b>B</b> .1 | RRC filters details                                          | 71 |

| B.2         | RRC filter implementation details.                           | 71 |

# **List of Tables**

| 5.1         | Available resources of ZC702's programmable logic (XC7Z020) | 48 |

|-------------|-------------------------------------------------------------|----|

| 5.2         | Generator spent resources and timing                        | 51 |

| 5.3         | RRCs' spent resources and timing                            | 53 |

| 5.4         | LINC calculator spent resources and timing                  | 54 |

| 5.5         | LINC LUT spent resources and timing                         | 55 |

| 5.6         | LINC implementations comparison                             | 55 |

| 5.7         | Original system's occupation                                | 57 |

| 5.8         | Complete system #1's occupation                             | 57 |

| 5.9         | Complete system #2's occupation                             | 58 |

| 5.10        | Occupation and comparison of all systems                    | 60 |

| 5.11        | Expected vs. final occupation results                       | 60 |

| <b>B.</b> 1 | FIR filter coefficients for $N_{sym} = 5$                   | 70 |

| B.2         | FIR filter coefficients for $N_{sym} = 7$                   | 72 |

| <b>C</b> .1 | LUT input addresses and corresponding output values         | 74 |

List of Tables

# **List of Acronyms**

| DAC    | digital-to-analog converter                    |

|--------|------------------------------------------------|

| ADC    | analog-to-digital converter                    |

| FIR    | finite impulse response                        |

| FPGA   | field programmable gate array                  |

| HPA    | high power amplifier                           |

| LSB    | least-significant bit                          |

| LFSR   | linear feedback shift-register                 |

| RNG    | random number generator                        |

| WFM    | waveform memory                                |

| SDR    | software-defined radio                         |

| CORDIC | Coordinate Rotation Digital Computer           |

| LINC   | linear amplification with nonlinear components |

| LUT    | look-up table                                  |

| FF     | flip-flop                                      |

| RAM    | random access memory                           |

| GPIO   | general purpose input-output                   |

| MM     | magnitude modulation                           |

| MPMM   | multistage polyphase magnitude modulation      |

| NL     | non-linear                                     |

#### List of Tables

| OQPSK | offset quadrature phase shift keying                              |

|-------|-------------------------------------------------------------------|

| PAPR  | peak-to-average power ratio                                       |

| RC    | rectangular clipping                                              |

| RMM   | ring-type magnitude modulation                                    |

| RRC   | root raised cosine                                                |

| PLL   | phase-locked loop                                                 |

| VCO   | voltage controlled oscillator                                     |

| HDL   | hardware description language                                     |

| VHDL  | Very high speed integrated circuits Hardware Description Language |

| JTAG  | Joint Test Action Group                                           |

| LED   | light-emitting diode                                              |

| MUX   | multiplexer                                                       |

| SC    | single-carrier                                                    |

| RF    | radio-frequency                                                   |

| SoC   | system on chip                                                    |

| ASIC  | application-specific integrated circuit                           |

| DSP   | digital signal processor                                          |

| MAC   | multiply and accumulate                                           |

| PS    | processing system                                                 |

| PL    | programmable logic                                                |

| FMC   | FPGA mezzanine card                                               |

| LPC   | low-pin count                                                     |

| FIFO  | first-in first-out                                                |

| HLS   | high level synthesis                                              |

- **RTL** register-transfer level

- **UART** universal asynchronous transmitter/receiver

- MIMO multiple input, multiple output

- **FFT** fast Fourier transform

- **USB** universal serial bus

List of Tables

# Introduction

#### 1. Introduction

The need for information in our world grows as a daily basis, and it is mainly supported by Telecommunications. This rising demand is targeting the focus of communication engineers to optimize power and spectrum efficiency and transmission rates, while minimizing systems' costs [2]. In the design of generic wireless radio-frequency (RF) transmitters, one of the components that need most attention is the high power amplifier (HPA), since it is a critical component [3]; the HPAs (that can perform linear or non-linear amplification) have direct influence on the overall cost, efficiency, bandwidth and linearity of the transmitter.

However, although the HPA component has such an importance to the transmission system, it does not mean that all the possible improvements that can be made have to be implemented on the HPA itself; the delivered signal has also an important role on the overall system performance. In fact, the signal's characteristics dictate HPA's features: while constant envelope signals allow for the use of low-cost power efficient non-linear (NL) amplifiers, typical modulated signals, with high spectral efficiency, present large envelope fluctuations (i.e. an high peak-to-average power ratio (PAPR)) and so require the use of expensive linear HPAs with poor power efficiency [3,4] in order to avoid signal distortion at the amplification stage. This way of thinking opens a vast set of solutions on signal conditioning (like PAPR reduction or envelope-control techniques [5,6]), and linear amplification with nonlinear components (LINC) decomposition [7] fits easily in these requirements.

The LINC [3, 8] technique consists on decomposing a signal in two phase-modulated signals (or branches) that have lower linearity requirements than the original; due to this, the branches can be effectively amplified by NL amplifiers. This decomposition is clearly an advantage over sending just the original signal without any processing because the system can now benefit from low-cost and efficient signal amplification, rather than expensive linear amplifiers. The NL amplifiers are cheaper, have higher amplification capacity than linear amplifiers [4, 9], and are much more efficient. The original signal can be reproduced again by combining the two LINC branches, taking into account that they need to be synchronized and balanced [3,7].

However, LINC is greedy in terms of spectrum [3], since the decomposition itself mirrors the envelope of the original signal: a highly variable input produces outputs with high phase content, which also contributes to spread the signal's spectrum. On the other hand, decreasing the decomposition angle  $\theta$  to lower values can indeed increase the LINC combination system efficiency [1]. Besides this, the LINC technique has some nuances when implemented in digital domain: the non-linear phase variation of their branches produces spectral regrowth, which is not desirable; for that reason, a high oversampling rate is included in the system in order to minimize this effect. However, an *a priori*

excursion limiting on the LINC input signal can effectively reduce the high oversampling requirements.

So, the objective at this point is to emulate at most an amplitude-limited signal, in both upper and lower bounds. The modulation that is closer to bring such results *per se* is OQPSK, which has a controlled envelope and smooth transitions, evades zero-crossing and produces an inside gap. Choosing a modulation like OQPSK could be a severe limitation for any current transmission system, since it has low spectral efficiency; however, Dinis *et al.* [10] shows that any signal from a high-order spectral efficient modulation can be seen as the sum of several OQPSK signals, so LINC limitations can actually be easily surpassed without compromising transmission efficiency, and the LINC concept itself can then be extended to high-order constellations. In fact, the proposed schemes are considered as valuable solutions for improving power efficiency of next-generation millimeter-wave communications where the use of multiple NL amplifiers and antennas is foreseen [11].

Every transmission system of this type needs a pulse shaping filter (usually a root raised cosine (RRC) [12]), in order to make the transmitting signal more adequate to the communications channel, e.g., by limiting its bandwidth. An OQPSK, when filtered by such a structure - that contributes to elevate the signal's PAPR - looses a part of its characteristics, namely the shape of the upper and lower bounds of the signal. One way to evade this problem is to apply ring-type magnitude modulation (RMM), which arranges the signal in a way that when it is passed by the RRC, the output assumes a ring-type form, generating a properly conditioned input for LINC. The RMM technique does not affect noticeably the transmission performance nor does it spread the transmitted signal' spectrum, and can effectively reduce the PAPR and lower the bandwidth utilization [1].

So, a LINC system, applied through the amplification of bandwidth-limited OQPSK signals, can clearly benefit from a joint implementation with RMM [13], since RMM effects will improve the conditioning of the input signal to the LINC technique<sup>1</sup> and as so, there will be lower oversampling requirements posed by performing LINC's decomposition at digital domain, as well as improving LINC's efficiency at the combination stage.

But how should this set of techniques be implemented in practice? There are some possible ways such as: application-specific integrated circuit (ASIC)s, digital signal processor (DSP)s, simple field programmable gate array (FPGA)s or even FPGAs with an integrated processor (system on chip (SoC)s). Although all have strong and weak points. For this proof-of-concept, the chosen platform should have the possibility to make fast and accurate calculations, enough memory storage for all the look-up table (LUT) ta-

<sup>&</sup>lt;sup>1</sup>Nowadays, multilevel LINC transmitters are also being tested with promising results concerning efficiency on signals with high PAPR [14].

#### 1. Introduction

bles that may be implemented and, above all, the capacity to transmit two RF complex signals (with an operating frequency approximately at  $1.2GHz^2$ ), resulting from LINC decomposition. Based on these requirements, it is time to choose which platform to use.

ASICs are usually very specific, and as so they are optimized in terms of power or resource density [16]. However, this only makes sense when the application is already tested and approved, since a new modification in hardware presents superior costs than in other devices; due to this, ASIC design can be more expensive. In fact, although ASICs are known to be low-cost devices, this advantage only occurs because they are mass produced devices.

DSPs are very efficient and optimized processors when the main purpose is, for example, to implement a finite impulse response (FIR) filter: its optimized multiply and accumulate (MAC) structure provides a good option to choose from. Also, today's DSPs have simple and easy programming interfaces, and many have full MATLAB/Simulink [17] integration, as well as FPGAs do. However, some DSPs may not still be the best in class when compared to designs in FPGA that achieve massive parallelism [18]. Although current DSP technology is heading to parallel implementations of algorithms [19], it is still not enhanced as it is on FPGAs, which can imply lower processing speeds [18].

On the other hand, FPGAs provide the capability of designing a complete system from scratch, tweak it and perfect it according to the user's needs (power optimization, area, speed or timing) more easily than in ASICs [16]; also, they are optimized to process information in parallel at very high rates. In sum, FPGAs' programmable logic (PL) allows many degrees of freedom for the system designer. This is undoubtedly the best choice for a proof-of-concept, whose needs can be broad and varied [16].

For our real-time system, the implementation is not limited to low-level parallel processing, and, for example, a connection to a host PC can be an advantage, in order to implement a master-slave control system. This can be achieved with an embedded processor, which only a SoC can provide: full PL-processing system (PS) integration, where parallel processing is achieved by the PL (FPGA) and sequential computation is done by the PS (embedded chip). Ultimately, it is the best of two worlds in one place.

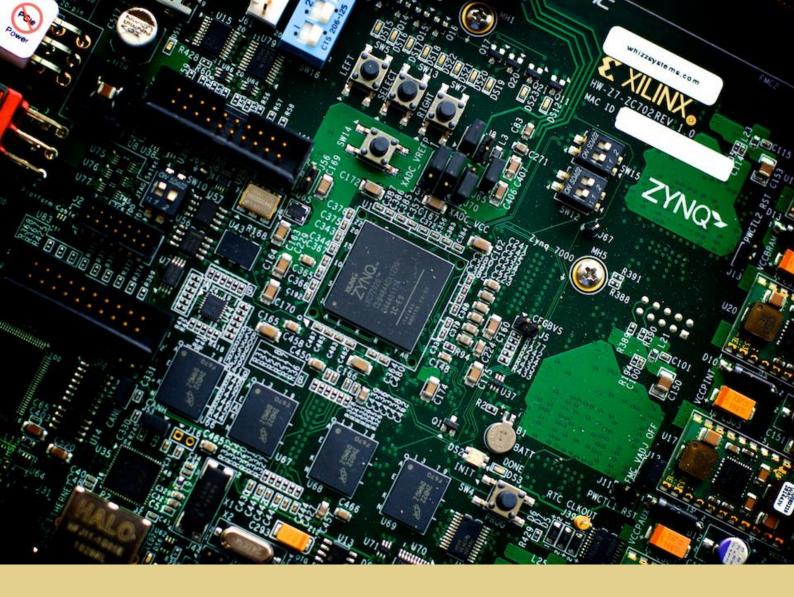

Consequently, the chosen platform was a SoC FPGA, more precisely a Zynq<sup>TM</sup>-7000 All Programmable SoC ZC702 [20] Evaluation Kit by Xilinx [21], due to its processing capabilities and connections. However, this board does not include any RF transmitters, which are essential to this proof-of-concept, but the existence of two low-pin count (LPC) FPGA mezzanine card (FMC)<sup>3</sup> connectors can surpass this problem, be-

<sup>&</sup>lt;sup>2</sup>This operating frequency was specified by project GLANCES [15], where a part of this thesis work is included.

<sup>&</sup>lt;sup>3</sup>FMC is an ANSI/VITA standard [22] I/O connection designed to increase modularity in FPGA systems. It was created to be used between FPGAs and daughter cards.

cause there are many FMC compatible daughter cards designed to transmit in RF that are ZC702-compatible. Taking this into account, and the RF transmitter frequency proposed (1.2*GHz*), our choice fell on two FMC30RF<sup>4</sup> [23] by 4DSP [24], on its frequency range variant from 1.2GHz to 3.0GHz. This board is compliant with the VITA 57.1 standard [22, 23] and has a DAC transmission (Tx) IQ modulator, with a bandwidth up to 30MHz per channel.

Since the chosen environment was a SoC, the signal's transformation will be fullydigital, which is an advantage due to the flexibility of digital systems over analog ones ( [3,25,26]). However, the LINC decomposition can be made both digitally or analogically [27,28].

Some implementations on FPGA were made concerning LINC [29] and magnitude modulation (MM) [30] <sup>5</sup> by using different approaches [31,32]. This work aims to present a full LINC-RMM transmitter, built on a Zynq-7000 architecture and employing different approaches rather than those widely used, with all the parameters optimized to get the most of the implemented techniques, in order to prove that such a system is a suitable candidate for highly efficient and low cost transmissions.

This thesis is also a part of an Instituto de Telecomunicações' investigation project GLANCES [15] which is the result of an intense collaboration between the Multimedia Signal Processing Group from IT-Coimbra and the Wireless Communications Group from IT-Lisbon, and whose final purpose is to investigate and create a power and spectrum efficient broadband wireless system, by studying signal processing methods and techniques like LINC and by building a complete communications system based on that. Besides the implemented transmission system, created in this thesis, an amplification system with LINC branches combiner will be built in hardware, in Lisbon.

### 1.1 Objectives

This thesis proposes to create a working prototype of a real-time system, built on a Zynq-7000 SoC architecture, that achieves a full RMM and LINC decomposition of any offset quadrature phase shift keying (OQPSK) signal, ready for transmission. Two different approaches to this problem were considered:

- 1. System with a LUT for both RMM and LINC blocks;

- 2. System with a LUT for the RMM block and a hardware calculation block for LINC;

<sup>&</sup>lt;sup>4</sup>Model: FMC30RF 2-1-2-1

<sup>&</sup>lt;sup>5</sup>This MM implementation was made by using its real-time variant MPMM, and not LUT-variant RMM.

Both systems will be detailed and compared in terms of performance, FPGA resources utilization and speed, in the subsequent chapters.

### **1.2 Dissertation Outline**

This thesis is structured in six chapters. After the introduction, LINC transmission systems will be explored in Chapter 2, and both MM and the used variant RMM will be explained in Chapter 3. Following these, a concise explanation of all the software and hardware architectures with some implementation choices will be given in Chapter 4, followed by a detailed description of the performed implementation and simulations in Chapter 5. Finally, Chapter 6 discusses the main results and conclusions derived from this thesis work and presents some ways to develop any future work on this subject.

### **1.3** Thesis framework and contributions

This thesis work was carried out under the project GLANCES [15] (Generalized Linear Amplification with Nonlinear Components for Power and Spectral Efficient Broadband Wireless Systems, supported by Instituto de Telecomunicações – IT). Also, it is the proof-of-concept of the developed work by Simões [1], and so, the best approaches considered by Simões will be applied here.

# LINC systems

The choice of HPAs to a generic wireless transmission system is very dependent of the requirements of power linearity, and it is known that linear HPAs have low energy efficiency [4,9] when compared to NL HPAs. The LINC technique [3,7,8] makes the use of highly efficient NL amplifiers in these transmission systems possible and still achieve linear power amplification.

This chapter is focused on the description of the LINC technique, on the possible ways to decompose a signal according to this method and the basics needed to implement such a system in an FPGA.

### **2.1** Basic concepts for LINC systems

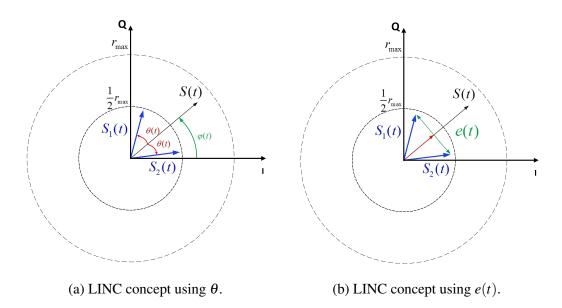

The LINC technique consists in decomposing a time-varying signal with non-constant envelope as a sum of two constant envelope phase-modulated signals. This decomposition can be made through two different representations: one is based on angle decomposition, and the other is based on vector decomposition.

Our starting point is the generic representation of a signal, S(t), which is given by:

$$S(t) = r(t)e^{j\phi(t)}$$

(2.1)

where both the instantaneous amplitude r(t) and phase  $\phi(t)$  vary with time. The timevarying amplitude can still be described as a constant amplitude phase modulated signal with an angle  $\theta(t)$ :

Figure 2.1: LINC decomposition technique using two different representations.

$$r(t) = r_{max} cos(\theta(t))$$

$$= r_{max} \frac{e^{j\theta(t)} + e^{-j\theta(t)}}{2}$$

(2.2)

where  $r_{max}$  is its maximum amplitude and  $\theta(t)$  is known as the LINC branches' decomposition angle, as depicted in Figure 2.1. From now on, both the decompositions can be derived from these main equations.

#### 2.1.1 Angle decomposition

The angle decomposition is very straightforward; merging 2.1 with 2.2, thus obtaining:

$$S(t) = r_{max} \left[ \frac{e^{j\theta(t)} + e^{-j\theta(t)}}{2} \right] e^{j\phi(t)}$$

$$= \frac{r_{max}}{2} \left[ e^{j(\theta(t) + \phi(t))} + e^{j(-\theta(t) + \phi(t))} \right]$$

(2.3)

From 2.3 it is possible to infer that S(t) has two distinct phase variations ( $\theta(t)$  and  $\phi(t)$ ), making it possible to describe 2.1 as the sum of two constant-envelope signals,  $S_1(t)$  and  $S_2(t)$ :

$$S_1(t) = \frac{r_{max}}{2} e^{j(\theta(t) + \phi(t))}$$

(2.4)

$$S_2(t) = \frac{r_{max}}{2} e^{j(-\theta(t) + \phi(t))}$$

(2.5)

where:

$$S(t) = S_1(t) + S_2(t) \tag{2.6}$$

as depicted in Figure 2.1a. As this derivation has no restrictions, it was proven that any signal can be described as a sum of two constant-envelope signals.

Computationally, in order to calculate LINC's branches, it is only needed to set a maximum value  $r_{max}$  and then compute the angle  $\theta(t)$  from 2.2, which is given by:

$$\theta(t) = \arccos\left(\frac{r(t)}{r_{max}}\right)$$

(2.7)

Always having in mind that  $r_{max}$  should be chosen as the maximum amplitude value that the signal can reach, or else some distortion will occur<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>A workaround to this problem will be discussed shortly.

However, regarding the implementation in the FPGA of the LINC angle decomposition, it is hard to calculate this solution, due to the computational weight of the arc-cosine function in conjunction with the implicit sines and cosines of Eqs. 2.4 and 2.5. Such a solution would spend at least two instances of CORDIC [33] blocks to perform these desired calculations<sup>2</sup>, since one instance only calculates one function.

#### 2.1.2 Vector decomposition

It is also possible to calculate the LINC branches via vector decomposition, where a vector  $1 \pm je(t)^3$  is defined as the transformation factor of S(t) in  $S_1(t)$  (plus sign) and  $S_2(t)$  (minus sign). Using the trigonometric identities:

$$cos(\theta) + jsin(\theta) = e^{j\theta}$$

(2.8)

$$sin(\theta) = cos(\theta)tan(\theta)$$

(2.9)

on Eq. 2.4, we obtain:

$$S_{1}(t) = \frac{r_{max}}{2} e^{j\phi(t)} \left[ cos(\theta(t)) + jsin(\theta(t)) \right]$$

$$= \frac{r_{max}}{2} e^{j\phi(t)} cos(\theta(t)) + j \frac{r_{max}}{2} e^{j\phi(t)} cos(\theta(t)) tan(\theta(t))$$

$$= \frac{r_{max} cos(\theta(t)) e^{j\phi(t)}}{2} \left[ 1 + jtan(\theta) \right]$$

$$= \frac{S(t)}{2} \left[ 1 + jtan(\theta(t)) \right]$$

(2.10)

A similar derivation can be made for Eq. 2.5, obtaining the following:

$$S_2(t) = \frac{S(t)}{2} \left[ 1 - jtan(\theta(t)) \right]$$

(2.11)

Regarding these mathematical expressions, it is easy to understand that e(t) is equivalent to  $tan(\theta(t))$ . Right now, the vectorial form seems to be no different of the angle form, since it also uses an angle expression to describe LINC decomposition. However, a closer look, with the aid of the mathematical expression:

<sup>&</sup>lt;sup>2</sup>CORDICs are the reference HDL building blocks to perform angle calculation (such as sines, cosines, tangents and their respective arcs), as well as square roots and polar-to-rectangular conversion and vice-versa.

$<sup>^{3}</sup>j$  the imaginary unit and e(t) an error vector that will be deduced shortly.

$$tan(\theta)^2 = \frac{1}{\cos(\theta)^2} - 1 \tag{2.12}$$

concatenated with the Equation 2.7, shows that e(t) can be described as:

$$e(t) = \sqrt{\frac{r_{max}^2}{r(t)^2} - 1}$$

(2.13)

dispensing the need of a direct angle calculation. Again,  $r_{max}$  should be previously defined in order to calculate this expression.

Since vectorial representation only needs to implement one CORDIC block for the square root (which in Chapter 5 will be compared to a simple memory unit (i.e., a LUT) in terms of resources occupation, for simplicity), it does not use as much FPGA area and resources as angle representation and it also allows to perform calculations with higher precision. For this reason, vectorial representation is the chosen type for our approach.

As it is mathematically proven,  $S_1(t)$  and  $S_2(t)$  have constant envelopes, and this lead to the possibility of using power-efficient non-linear amplifiers. So, indirectly, LINC decomposition increases the overall efficiency of a wireless transmission system.

#### 2.1.3 LINC branches matching

On the receptor side, both LINC branches can be added to generate an amplified replica of S(t). In theory, the signal  $S_{received}(t)$  would be a perfect copy of S(t); however in practice, this combination requires some care:  $S_1(t)$  and  $S_2(t)$  have to be perfectly synchronized and any unbalances between the transmitting branches can cause small deviations between the received signal and the transmitted signal.

The sets of equations (2.4) - (2.5) and (2.10) - (2.11) are mathematically equivalent; however, one of the sets may outperform the other in a digital implementation of the system, depending on how the two branches are physically generated [3, 25, 26]. As stated earlier, vectorial representation will tend to be the most used because the involved calculations are simpler and faster to execute on an FPGA<sup>4</sup>.

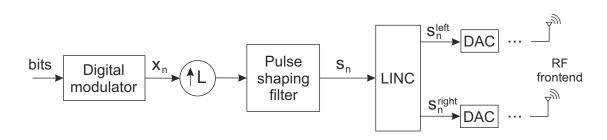

### 2.2 Digital LINC transmission system

As referred to in Chapter 1, this implementation will be fully-digital, which is a common choice [3, 25, 26] due to the offered flexibility. To contextualize, a generic digital LINC transmitter is shown in figure 2.2.

<sup>&</sup>lt;sup>4</sup>More on this topic will be presented in Chapter 4.

Figure 2.2: Basic digital LINC transmission system.

The entering information is assumed to be binary and it is coded by a digital modulator that shapes the input bits to output symbols ( $x_n$ ). After this, the signal is oversampled by a factor L and passed through an RRC filter (this process is usually called pulse-shaping, which limits digitally the bandwidth of the signal to transmit). Finally, the digital signal  $s_n$  (equivalent to S(t) in analog analysis) is ready to be decomposed by LINC, and then converted to analog to be amplified and transmitted.

The value of the oversampling factor L must be chosen wisely, since it will have direct effect on the signal spectrum of the LINC's components: an arbitrary choice that does not take the LINC's oversampling requirements [8] and the digital-to-analog converter (DAC)'s reconstruction filter into account and it may provoke peak regrowth, which is unwanted. A high oversampling rate avoid these problems, while lowers the needed complexity of this reconstruction filter, and in consequence, its cost [12].

As stated in Simões [1], the value of L was chosen to be 8, along with other important parameters for the design. This topic will be further discussed.

#### 2.2.1 Parameter-imposed limits

When talking about the LINC's discrete-time decomposition, it is needed to take into account the DAC features (reconstruction filter characteristics and resolution) and the HPAs' saturation effect of  $\theta(t)$  and e(t). These effects may compel the LINC's input signal  $s_n$  to be clipped. In this case,  $\theta$  and e are given by:

$$\theta(r_n) = \begin{cases} \arccos\left(\frac{r_n}{s_M}\right), & r_n \le s_M \\ 0, & r_n > s_M \end{cases},$$

(2.14)

$$e(r_n) = \begin{cases} \sqrt{\left(\frac{s_M}{r_n}\right)^2 - 1}, & r_n \le s_M \\ 0, & r_n > s_M \end{cases}$$

(2.15)

where  $r_n$  is the amplitude of the original digital signal, related to sample *n* and  $s_M$  is the LINC maximum amplitude level (or clipping level)<sup>5</sup>. As stated in [8], the polar clipping

$<sup>{}^{5}</sup>s_{M}$  is the digital-equivalent of  $r_{max}$ , on the previous analog analysis.

operation has a slightly superior performance, when compared to cartesian operation, this being the reason why polar clipping was chosen.

Assuming ideally balanced amplifiers and perfect combining, we can determine the transmitted signal  $s_c$  using the following equation (assuming an amplifiers' unit power gain):

$$s_c = s_{n1} + s_{n2} = \begin{cases} s_n, & |s_n| \le s_M \\ s_M e^{j \arg(s_n)}, & |s_n| > s_M \end{cases}.$$

(2.16)

As stated earlier, such a system requires enough bandwidth to accommodate both signal's components, while it needs a perfectly balanced branch amplification in order to cancel the complementary terms of  $s_{n1}$  and  $s_{n2}$ , because any possible amplitude or phase unbalances between the two branches may result in significant performance degradation [1,3,8].

# **Magnitude Modulation**

The HPA is a key component of the front-end of any RF transmission system, both for its role and for the great amount of energy it consumes. The spent energy can be lowered if proper conditioning is done to the transmitting signal, reducing the signal's excursion and, in consequence, its PAPR. On an OQPSK transmitting system that includes LINC and a RRC, the RMM implementation also takes a major role in signal conditioning, significantly improving the overall power and spectrum efficiencies. The RMM technique is then presented as a solution to improve system performance, because it offers the possibility to control the amplitude's upper and lower bounds, thus increasing energy efficiency for transmission without noticeable performance reduction, for any given input OQPSK signal.

This Chapter will explain the model of the RMM method for single-carrier (SC), thought to fit in the current transmission system.

### 3.1 The Magnitude Modulation Principle

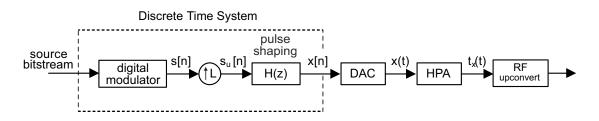

Figure 3.1 shows a typical SC transmitter, composed by its basic building blocks.

Figure 3.1: Generic SC transmitter scheme [34].

The pulse-shaping filter used to limit bandwidth is the main contributor for the transmitted signal high PAPR. In fact, as mentioned in Chapter 1, when the transmitted bits are mapped in constant-envelope constellations, it is the only contributor for the signal's PAPR. This effect makes room for a symbol readjustment operation to limit the signal's excursion (prior filtering).

Figure 3.2: Magnitude modulation principle [34, 35].

The principles of MM are shown in more detail in Figure 3.2. The technique conjugates the knowledge of the pulse-shaping impulse response with the awareness of the signal being transmitted, with the magnitude modulation factor m[n] that is applied to each symbol s[n] being computed, taking into account s[n]'s closer neighbors.

Currently, there are two major techniques that are used to apply MM: one is the realtime calculator MPMM, which implements the RRC on its polyphase representation. In this method, the MM is as a cascade of basic blocks, as depicted in Figure 3.3, and only the current symbol is considered for a MM calculation. The other case is the pre-calculated LUT-based MM, whose implementation is reduced to a simple memory access<sup>1</sup> and in which a sequence of 2D + 1 symbols is used to calculate only one MM coefficient - the quantity of used symbols to calculate just one coefficient explains the complexity of the process and the difficulty of implementing it in real-time.

Figure 3.3: MPMM system.

Since the real-time computation of the multistage polyphase magnitude modulation (MPMM) coefficients require high processing rates and FPGA resources, the implemented system would not benefit much nor would it be capable of having a MM calculator over a LUT-based approach, due to the fact that the LUT system is far more efficient in terms of speed and occupied resources.

But, when talking about OQPSK signals, a different MM scheme can be applied, which is more adequate and provides PAPR reduction: it is the RMM. This technique is very similar to the MM-LUT, having just one difference: in this case, a lower bound to the signal's amplitude is also implemented, in order to decrease the decomposition angle

<sup>&</sup>lt;sup>1</sup>Since the calculation of the MM coefficients is computationally heavy and complex, a real-time version of MM currently makes no sense.

$\theta$  and thus, prepare the signal for a more efficient LINC decomposition and addressing its requirements, after pulse-shaping filtering. In our case, this method will be used by employing a static memory (LUT) in the FPGA.

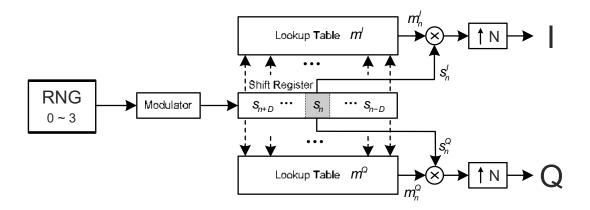

## 3.1.1 Look-Up Table Based Approach

The LUT-RMM method relies on a previous computation of all the coefficients, so that the true effort of a system which implements this method becomes reduced to a memory access. Figure 3.4 shows the implemented MM block, where 2-bit symbols enter sequentially to the current set.

Figure 3.4: Generic LUT-based Ring-type Magnitude Modulation transmitter scheme [1].

The process of creation of the LUTs is described on Algorithm 1:

Algorithm 1 Concise Algorithm for Computation of RMM Coefficients' LUT [34].

**do** {

STEP 0: Setup input data.

| Input Data = $\begin{cases} \\ \\ \\ \\ \\ \end{cases}$ | Signal to be MM                   | $\Leftarrow$ | first iteration  |

|---------------------------------------------------------|-----------------------------------|--------------|------------------|

|                                                         | MM signal from previous iteration | $\Leftarrow$ | other iterations |

STEP 1: Filter data using a RRC filter.

STEP 2: Limit the magnitude of the filtered signal to the specified thresholds  $A_l$  and  $A_u$ .

STEP 3: Filter the resulting signal using a match RRC filter.

STEP 4: Sample the resulting signal to obtain the RMM sequence corresponding to the input data.

} while (Signal limitation occurs in STEP 2)

STEP 5: Output the RMM coefficients by performing the ratio of RMM signal from the most recent iteration to the input original sequence to be RMM.

In this algorithm, a channel with noiseless transmission is emulated. The starting MM sequence is an all-ones vector, so that the algorithm's first iteration does not include MM. Then, the input sequence is upsampled, filtered through an RRC and evaluated according to the algorithm's clipping method. After this, the output signal is filtered again in a matched RRC, and the corresponding symbols to the input data are obtained through sampling. Finally, the quotient between the output and the input sequences is computed, and this ratio is stored as a MM coefficient. The iterations are repeated until no more clipping is applied.

# 3.2 Ring-type Magnitude Modulation applied to OQPSK signals

The original MM procedures only limit the signal's envelope maximum excursions, since their appliance is made in SC transmissions that employ linear HPAs. However, by using LINC techniques on the system, energy efficiency of the front-end is mainly limited by the combiner's efficiency [3, 36]. According to Simões [1], a reduction of the decomposition angle  $\theta$  can effectively increase the combiner's efficiency and reduce the signal's PAPR. This can be translated to a lower bound limiting on the LINC input signal's amplitude.

The RMM technique appears as an effective excursion control method that can fit those requirements: its lower and upper bounds limiting helps generate a properly conditioned input for LINC, while not diminishing the transmission's performance. However, it would be desirable to have an initial signal that could be as approximate to these requirements as possible, in order to simplify the modulation methods. OQPSK appears as the best candidate, since it has an upper and lower limited envelope, that evades zero-crossing and has smooth transitions.

This technique was thought to fit a transmission system, which includes a pulseshaping filter (an RRC in this case): the final ring-shaped form is only obtained after filtering, i.e., where the LINC decomposition technique is applied.

#### 3.2.1 LUT scheme

The modulated symbols are stored sequentially in an array, with a total capacity of 2D + 1 symbols. When symbol s[n] is first stored, it is used with the previous 2D samples to calculate the amplitude factor of the symbol s[n - D], which is the current middle symbol of the stored set, , i.e. the LUT-MM scheme introduces a processing delay of D symbols. After this computation, all symbols advance one position in the stored array,

including s[n], thus making space for one new symbol, that is s[n+1]. Now, the scaling factor obtained is multiplied by s[n-D+1], and the cycle continues endlessly. It is easy to comprehend that for any finite D length and bits to represent a symbol, there will be a limited number of possible cases, and in consequence, a limited number of scaling factors. So, for a constellation with M symbols, this number of factors is equal to  $M^{2D+1}$ , which is equal to the number of entries of the necessary LUT to implement.

The value of D is not arbitrary; it should be chosen accordingly to the RRC filter's characteristics, namely roll-off and length, to make sure that all the symbols that contribute for the signal's amplitude are included in the calculations. The filter's length is given by the following expression:

$$length_{RRC} = 2 * N_{sym} * L_{oversampling} + 1$$

(3.1)

where  $N_{sym}$  is the number of considered symbols and  $L_{oversampling}$  is the oversampling factor<sup>2</sup>. In order to perfectly match the designs of the RRC and the MM LUT, the number of affected symbols must be the same; this means that  $N_{sym} = D$ . However, an implementation of the RRC filter with a value of  $N_{sym}$  superior than the perfectly-matched can also bring similar results <sup>3</sup>.

As this technique requires D symbols to be stored *before* they are actually used, the RMM block inserts a time delay that is equivalent to the symbol time  $T_{symb}$  multiplied by D symbols.

#### **3.2.2** Table size and parameters

As stated earlier, considering a LUT-MM memory of 2D + 1 symbols and a constellation of size M, the computed MM LUT will have  $M^{2D+1}$  entries. In our case, D was chosen to be equal to 3, in order to have a reasonable contrast between the LUT states and not an enormous table, to acknowledge system's timings and resources. Also, the implemented constellation is an OQPSK<sup>4</sup>, which leads to an M factor equal to 4; the constellation size can never be neglected since it greatly affects the overall length of the generated LUTs. These values originate two 16384-entries LUTs (one for I and one for Q), where is being employed rectangular clipping (RC).

Regarding the RRC implementation with a specification of having a roll-off factor of 25%, a filter was designed (spreading over 7 past and future symbols) and an oversampling factor L = 8.

<sup>&</sup>lt;sup>2</sup>Note that the length of the RRC filter is always odd.

<sup>&</sup>lt;sup>3</sup>It is taken as example the study made in Simões work [1], where D = 5 and  $N_{sym} = 7$ , without any loss of performance; more on this topic will be developed on Chapter 5, Sub-chapter 5.2.2.

<sup>&</sup>lt;sup>4</sup>Refer to project GLANCES [15].

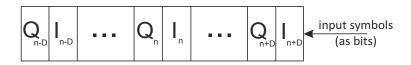

#### 3.2.3 Symbol storage and search

The way symbols enter the shift-register is intrinsically connected to the MM table algorithm. In the current case, and due to the method used to create the LUTs, any new symbol is appended on the right, and all the symbols are composed by their quadrature component (Q value), followed by their in-phase component (I value), in a right-to-left scheme, as stated in figure 3.5. This value is implicitly casted to a 14-bit unsigned integer (i.e., 2D + 1 times 2 bits/symbol), being the bit  $I_{n+D}$  the least-significant bit (LSB); this 14-bit number is used as the input of the RMM LUTs, which gives the corresponding coefficients to be multiplied by the current middle symbol.

Figure 3.5: Considered buffer scheme.

#### 3.2.4 Final acknowledgments

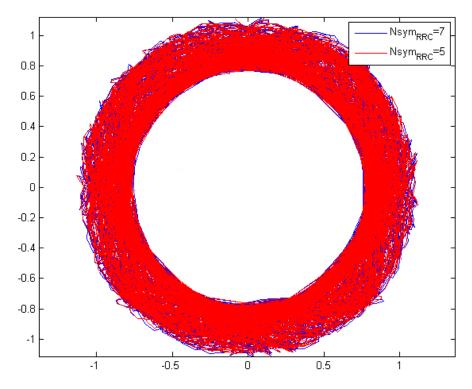

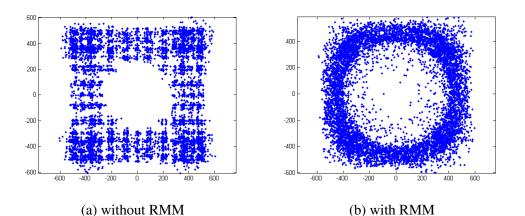

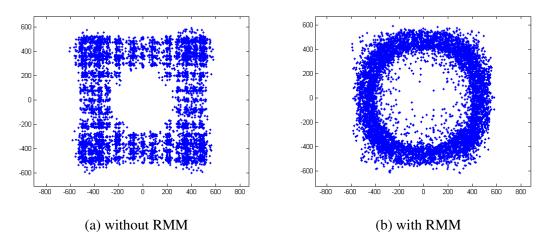

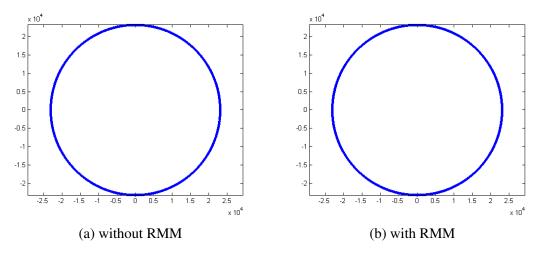

The expected result of ring-type magnitude modulation on an OQPSK modulated signal is illustrated as an example in Figure 3.6 ([1]). It is shown that the samples that overpass the imposed amplitude threshold are uniformized and that the inner gap is wider.

Figure 3.6: Diagrams of the transition path between the constellation's symbols of a ringtype magnitude modulated OQPSK signal without RMM (3.6a) and with RMM (3.6b).

According to Simões [1],  $A_l$  and  $A_u$  will be set to 0.8 and 1.1 (which are the applied thresholds on Figure 3.6b), respectively; this choice is corroborated by Simões work [1] on LINC acceptance of various lower and upper bounds testings.

# 3. Magnitude Modulation

#

# **Architecture Design**

#### 4. Architecture Design

In the previous chapters, both LINC techniques and RMM were theoretically explained, always having in mind the final purpose of this thesis. However, some developments and equations that seem rather easy to develop in theory, become quite complex to implement on FPGAs (for example, LINC angle representation would require CORDIC blocks to compute sines, cosines and arc-tangents, which are more resources consuming than vector's representation, which only needs a square-root calculation). Also, it is always necessary to know that all the resources are limited, which conditions the development of optimal code to maximize operation speed and minimize the occupied area.

This chapter aims to explain the developed implementation, both in hardware terms (devices used and testing workspace) and in software terms (utilized programs and implementations). This chapter opens the way to Chapter 5, where a more complete overall implementation will be discussed, along with the obtained results.

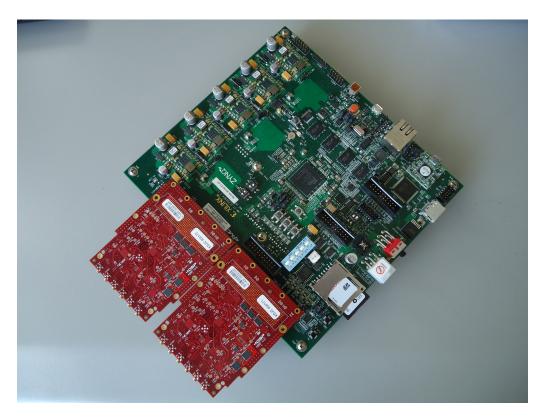

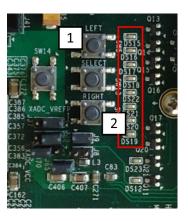

# 4.1 Hardware and Workspace

As referred to in Chapter 1, some generic requirements would be necessary (e.g. high processing power and speed), in order to accomplish all the stages of the transmission system correctly. The selected board was a  $Zynq^{TM}$ -7000 All Programmable SoC ZC702 [20] Evaluation Kit by Xilinx [21] <sup>1</sup>, with two FMC30RF<sup>2</sup> boards [23] by 4DSP [24], on its' frequency range variant from 1.2*GHz* to 3.0*GHz*, because the system was thought to be operating with a 1.2*GHz* carrier RF frequency<sup>3</sup>. A photo of the utilized boards is shown in Figure 4.1.

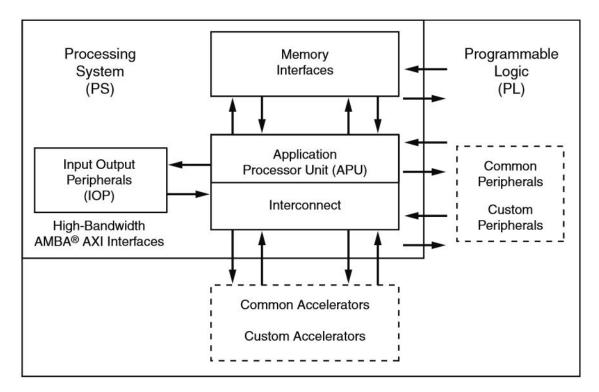

#### 4.1.1 ZC702

The ZC702 is the main board of the hardware setup: it is here that all implementations are deployed and whose physical resources are used. The ZC702's features include a JTAG interface for communication and bitstream upload, an Ethernet interface via a RJ-45 connector, a USB-to-UART bridge, an  $I^2C$  bus [37], two FMC LPC connectors, 1GB DDR3 component memory and general purpose input-output (GPIO); also, the SoC contains an integrated PS and PL (depicted in Figure 4.2), whose both parts run independently and the PS holds two ARM Cortex<sup>TM</sup>-A9 application processors, internal memories and external memory interface and peripherals such as the ones mentioned above. This thesis will only step through the most relevant board details; however, a more complete description is available in [38].

<sup>&</sup>lt;sup>1</sup>Zynq SoC device reference: XC7Z020-1CLG484C.

<sup>&</sup>lt;sup>2</sup>Model: FMC30RF 2-1-2-1.

<sup>&</sup>lt;sup>3</sup>From now on, the selected FPGA will just be called ZC702, and the daughter cards will be called FMC30RF, for simplicity.

Figure 4.1: Board set.

This board's PL has a 200MHz system clock source and programmable user clocks. For the implemented design, a 100MHz clock is generated to feed all the hardware components. Also, it has a PS clock source, working at a frequency of 33.3MHz. Our system will be completely developed inside the PL, since all the created blocks work in VHDL.

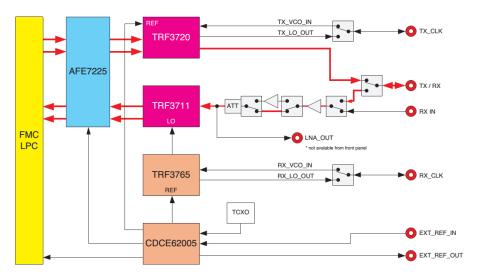

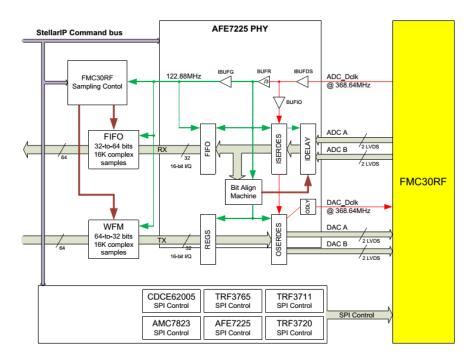

#### 4.1.2 FMC30RF

The FMC30RF boards are RF transceivers with a dual DAC transmitter IQ modulator with up to 30MHz bandwidth for each channel<sup>4</sup> and a dual analog-to-digital converter (ADC) receiver IQ demodulator, with an on-board PLL/VCO. The DAC offers a transmission rate up to 250Msamples/s with a 12-bit precision. A high level block diagram is shown in Figure 4.3, and a broader description of this board is available in [40].

The original firmware schematic of the board is also presented, where the created structures are depicted with more detail, like the reception FIFO or the transmission WFM, which is a memory block used to store the values before transmission. This block works like a FIFO, but with slight differences: here, the values are only refreshed if a direct command is sent to the block. While that does not happen, the WFM keeps send-

<sup>&</sup>lt;sup>4</sup>Although 4DSP announces up to 60 MHz of bandwidth, this value is a sum of both the I and Q bandwidths, as stated in [39].

Figure 4.2: High Level Block Diagram of Zynq-7000 XC7Z020 AP SoC.

Figure 4.3: High Level Block Diagram of FMC30RF.

ing the same set of data continuously, working as a circular FIFO. This could become a problem if the objective is to generate a transmission channel; however, it has a simple solution, as it will be discussed in Sub-chapter 4.2.5.

Figure 4.4: FMC30RF supplied firmware schematic.

### 4.1.3 Other equipment

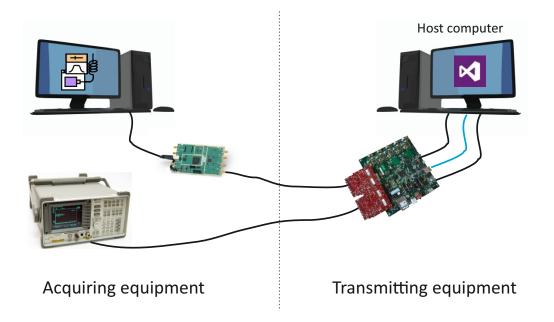

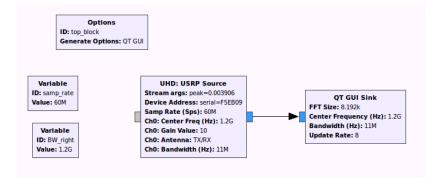

Besides the above mentioned boards, some equipment was used to test and acquire the output signals, namely an HP 8591E Spectrum Analyzer, which has a range that covers the chosen RF transmission frequency, and a USRP B210 software-defined radio (SDR) board [41], which is a transceiver board that also supports the reception of the desired frequency. Both equipments present evaluations in real-time. Host computer-board interaction was also used to acquire directly the generated data from the RRC and LINC blocks' outputs, which is considered to be more reliable to see if the blocks are working correctly.

The hardware setup is depicted in Figure 4.5. The first equipment was used to analyze the spectrum and test in part the validity of the output signals that came from both FMC30RF boards (LINC branches), and the second one was used to see the same outputs, but in both time and frequency domains and the constellation of the signal. While the spectrum analyzer requires no software, the USRP board needs a host computer with USB<sup>5</sup> that runs GNU-Radio [42]. GNU-Radio is an open-source software that works

<sup>&</sup>lt;sup>5</sup>Preferably, USB 3.0 or better to provide decent dataflow speeds (USB 2.0 will also work).

Figure 4.5: Complete diagram of the hardware setup.

based on a programming block environment to manage compatible SDR boards. However, since this material was only used to measure and acquire some signals' elements, a detailed explanation on its working will not be given on this thesis.

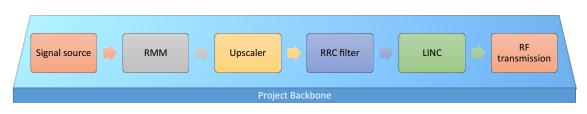

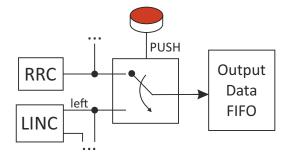

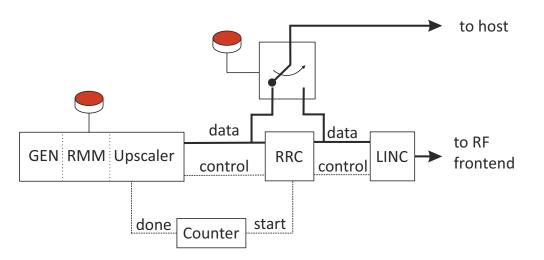

# 4.2 System Architecture and Implementations

The focus of this work is to build in FPGA an efficient OQPSK transmitter system with its power efficiency leveraged through the use of RMM and LINC amplification techniques. Figure 4.6 shows the architecture of this system, that is composed by: a pseudo-random OQPSK symbol generator, the ring-type magnitude modulation block, an upsampler and the pulse-shaping RRC filter, the LINC decomposer and a transmitter front-end that is capable of reproducing the two output branches of LINC. Ideally, a signal sink connected to some of these elements would be an advantage, since it would allow capturing intermediate values, for more accurate testings. This evaluation will be performed by connecting the outputs of the "transmission via RF" block to the acquiring equipment previously mentioned.

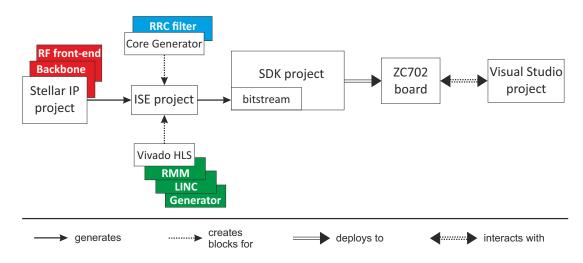

Hardware implementation was mainly supported by software tools; like most of the actual platforms on the market, each of the above described hardware parts have a proprietary software included to increase systems design's speed. The manufacturers of FMC30RF offer a software which is compliant with one of the available design suites from Xilinx, so software compatibility should not be a problem. For the different stages

Figure 4.6: Projected data flow.

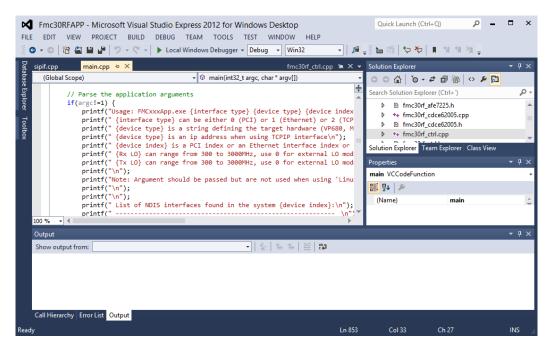

of this design, the used programming/software languages were VHDL in Xilinx ISE [43], C/C++/System C in Vivado HLS [44] and in Visual Studio [45], and the block-based programming Stellar IP [46]. Since several different programs were used during the designing process, a simple schematic is presented on Figure 4.7 to unveil a small part of all the stages that have been undertaken.

Figure 4.7: Complete software schematic of the design process.

# 4.2.1 Project backbone - Stellar IP

The starting point of the transmitter' software architecture is the base firmware that came with the FMC30RF boards - a Stellar IP project. This project does not really program anything; it simply creates the backbone of the complete project, and arranges the fundamental building blocks of the design, like the hardware description language (HDL) files which configure the hardware of the FMC boards or the ZC702 main board. This part can be seen as the lowest level in programming terms, since these blocks describe directly the utilized hardware structures. Stellar IP<sup>6</sup> is a proprietary software, produced by 4DSP, that builds a Very high speed integrated circuits Hardware Description Language (VHDL) project from their building blocks environment.

<sup>&</sup>lt;sup>6</sup>Version used: 1.2.0.0.

#### 4. Architecture Design

#### **Stellar IP**

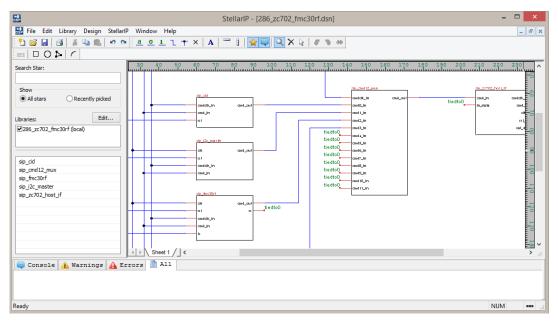

The workspace is depicted in Figure 4.8; it is very clean and simple, and it functions in a pick-and-place way: the system designer only needs to select the necessary components, drop them in the main design window from the left pane of blocks, and finally wire them. However, this simple aspect can be tricky to a newcomer: errors are not well documented, and the tool itself provides almost no feedback on how to solve them. For example, the simple act of putting an extra block and connecting it correctly on any original design will trigger an error, unless some intrinsic parameters are altered before this change.

Figure 4.8: Stellar IP workspace.

The original Stellar IP project was prepared to receive the transmitting signal from the host computer to the board via Ethernet, and to send the acquired signal from the board to the host via the same protocol, which is equivalent to say that, originally, the signal source would be the host computer. However, the boards producer states that the original firmware does not support very high downlink speeds and may not be reliable in timings as the designer wishes [47], which is a major weakness if working at high clock frequencies is a necessity. Because of this situation, our design method was rethought and the employed solution was to generate a signal's source in VHDL to be implemented inside the main board, i.e., the ZC702. This would solve any possible timing problems, since it is the board itself that is generating the input, instead of an external source.

In addition, the original firmware was only designed to handle a single FMC daughter card with a single ZC702 board, with one RF reception and one RF transmission channel. But, in our case, two output branches are needed for LINC; a single FMC30RF card is

not able to emit them simultaneously, so two boards are needed. This was indeed the principal and most challenging alteration made on the original design: add a second FMC block and connect it to the rest of the diagram, working with both the transmission and reception channels - this is the design flow of a multiple input, multiple output (MIMO) system.

However, in order for this diagram to work, more than 100% of the available resources of the ZC702 would be needed, which means that the MIMO system would not be feasible. So, a workaround was employed: since the important part of a transmitter is its transmission channels, the receiving ports of both the boards were disconnected from the main board, thus deactivating for now the entire reception part on the block diagram.

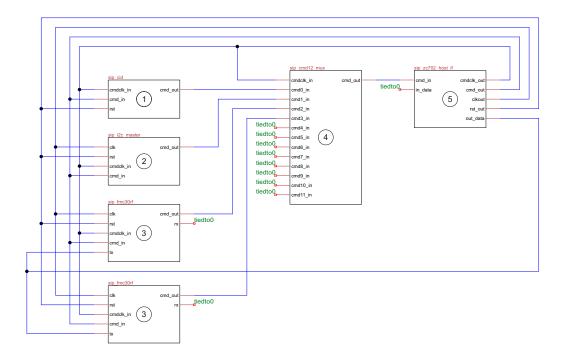

#### **Block diagram**

Figure 4.9 depicts the final block diagram achieved in Stellar IP for this system. As mentioned, there were two FMC30RF parts (3) used, a ZC702 part (5), and some control parts: a command multiplexer (MUX) (4) where the control signals of all the blocks are multiplexed, in order to connect them to the ZC702; an  $I^2C$  [37] master (2) which handles some control signals of the ZC702 board itself; and a block to store all the necessary info about the design like the number of blocks or their memory indexes: the Constellation ID block (1). It is possible to observe in the FMC30RF blocks that the *rx* pin is disconnected, to accomplish the deactivation of the reception part of the design. The *rx* port handles the FMC30RF's gathered values from the ADC.

As it can be seen in Figure 4.9, the transmitting ports of the FMC30RFs are connected to an output port of the ZC702 board, which means that, by now, the main board is considered to be the signal source for our future design. This topic will be further evaluated.

When it is completed, the design can then be generated and a VHDL project is built, to be used in Xilinx ISE software [43]<sup>7</sup>.

#### New structures placing

Once the fundamentals of the transmitter are concluded, the software blocks (RMM, RRC and LINC) can then be developed. The obvious place where these structures should be inserted is between the signal source and the transmitting port of the FMC30RF. But first, more important questions arise: these implementations should be described in VHDL, in order to fit in the existing backbone, but building such complex designs

<sup>&</sup>lt;sup>7</sup>Although Xilinx has already a newer and more complete suite of design tools, i.e., Vivado Design Suite [48], Stellar IP does not support Vivado project generation for any FMC30RF design, neither the company plans to support it in the near future whatsoever [49].

Figure 4.9: Generated Stellar IP design.

in VHDL by hand would be very problematic, even if the designer has solid skills in hardware description languages.

Fortunately, there are some tools that automatically construct VHDL blocks from a set of existing designs from where the user can choose, like Xilinx Core Generator [50], that are very optimized and are widely used (like filters, FFT blocks or FIFOs). In case the designer wants something very specific, and because of that it is not available in these predefined libraries, there are some other tools that can build VHDL structures from code in other languages, such as C or C++; these are the high level synthesis (HLS) tools, and in this case, a wide range of software is available, such as Xilinx Vivado HLS [44], Bluespec [51] or PandA [52].

In our transmitter's case, both these needs apply. Since an RRC filter in our design is needed, a tool, as the first type mentioned, is used, which is the Core Generator [50]. Also, the offered set of designs from Core Generator do not hold blocks that perform neither LINC decomposition nor RMM, so for these implementations, a second-like tool will be used: Vivado HLS [44]. Both these tools are developed by Xilinx, this being the main reason of their choice, to avoid having integration problems.

#### 4.2.2 RRC filter - Core Generator

The pulse-shaping filter, in this case an RRC, is one of the key elements of any RF transceiver, since it limits the signal bandwidth and adapts it to the characteristics of

the communications channel, in the digital domain. Filters are common components of communication systems (and signal processing systems in general), and thus they are already built and optimized to be synthesized in hardware. Indeed, Core Generator [50] has a FIR filter implementation in its library, so it is only necessary to personalize it according to our needs.

In our architecture, an OQPSK-modulated complex signal is provided at the entrance of this block, and so the filter has to employ two single-rate channels (one for the inphase component and another for the quadrature). In Sub-chapter 3.2.1, an explanation was given on the relation that should exist between the number of taps to implement on the filter and the quantity of affected symbols from the RMM: the RMM LUT tables size should follow the number of the filter's  $N_{sym}$ , which in our case is equal to 7. However, Simões [1] used an RMM table with just 5 affected symbols, since a table with 7 affected symbols would have a size of approximately  $10^9$  entries (refer to Sub-chapter 5.2.2) and is computationally extremely heavy to create. This shrink of the RMM tables was successful, because there was not any apparent loss of performance in his system.

In our case, and since the tables are being implemented in an FPGA with limited resources, even the use of RMM LUT tables with 5 affected symbols was not feasible, since it occupied more than 100% of the ZC702 LUT's resources; this problem motivated a new reduction in the size of the RMM tables, using just 3 symbols, instead of 5 used by Simões [1]. This increased gap between the number of affected symbols by the RRC filter and the RMM LUTs motivated some testing, to understand if an RRC filter with the factor 7 and the RMM implementation with the factor 3 would work well together, or if instead a filter with a lower factor, i.e. 5 affected symbols, would perform better, due to the smaller difference between factors. The resulting comparisons show that the smaller RMM table implementation was successful and that both filters perform similarly; the results are presented on Sub-chapter 5.2.2, whose filters' details are shown in Annex B.

#### **Filter implementation**

Therefore, regarding the filter implementation, Simões [1] approach will be followed: the implemented filter will have 113 taps, generated in MATLAB [17] with a roll-off factor of 25%. The FIR block also offers the possibility of upsampling the input sequence by a constant factor, which would be desirable; however, this upsampling does not support OQPSK, since it is not possible to specify a time shift between the implemented single-rate channels, i.e., the in-phase and quadrature components. Because of that, the upsampling is performed outside the RRC filter block.

Finally, at the input, a set of two fixed-point signed values are expected (one for I and

one for Q) with a format of  $Q4.18^8$ , and all the calculations inside the block are done in fixed-point arithmetics: the coefficients are stored in a fixed-point format of Q0.16 in a complements of 2 arithmetic. At the output, signed Q7.9 values are expected at each channel, and an output rounding mode of truncating LSB is performed.

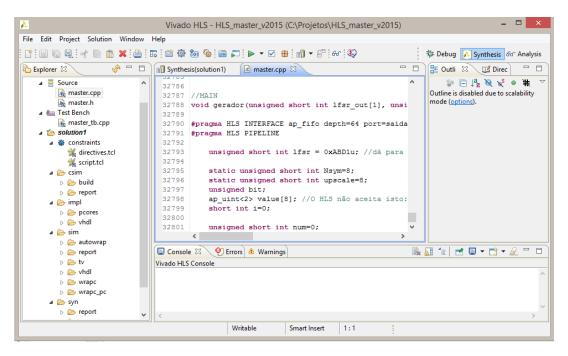

## 4.2.3 LINC and RMM - Vivado HLS

Due to their specificity and novelty (as for RMM), the core blocks of our transmitter, namely LINC decomposition and RMM, are not implemented in the Core Generator libraries; the same happen to the OQPSK signal source and the upsampler, which need to be implemented to surpass the original system limitations. A solution that is followed is to create them in Vivado HLS v2015.2, which is a C-to-HDL synthesizer [44]. Using this type of tools, much time can be spared in system designing over direct VHDL writing, because whether the design is big, complex or hard to describe in hardware language, the software will automatize all the programming sequence and build an accurate machine model, discarding the user of all this work.

#### Vivado HLS

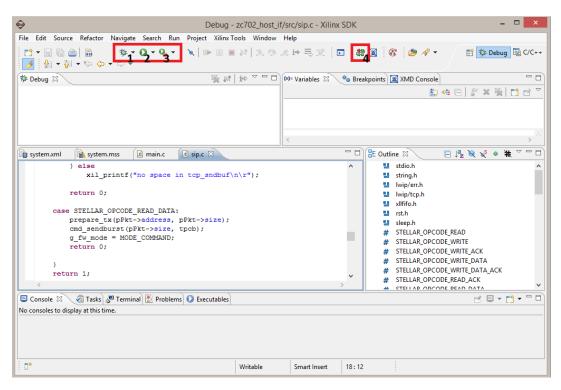

Vivado HLS workspace is shown in Figure 4.10. On the left pane, there is a file explorer of the open project, and in the middle is the language editor.

Figure 4.10: Vivado HLS workspace.

<sup>&</sup>lt;sup>8</sup>Notation: Q *Bits*<sub>Integer</sub>.*Bits*<sub>Fractional</sub>.

On top (refer to Figure 4.11 to better understand this explanation), it is possible to synthesize the code (2), to run a C simulation (1), to co-simulate C and RTL (3) for a more precise report on the behavior of the design, and to export the design (4), so it can be used on ISE [43], for example. All these actions, except the last one mentioned, produce a block and timing report in terms of clock cycles, function of the board operating frequency/period, chosen in the project properties. These reports detail the main resources and the minimum amount of time that the block needs to function properly, and so they are very important to the designer since it is possible to preview if one block will fit the main design constraints or not.

Figure 4.11: Vivado HLS main action buttons.

#### **Implemented blocks in Vivado HLS**

In this thesis, three different blocks were built in Vivado HLS [44]. The first two refer to the LINC decomposer, comparing two different approaches in terms of speed and calculations accuracy in the implementation of the vectorial decomposition equations (see Section 2.1.2). The first block performs it by calculating all the stages, while the second uses a LUT where the calculation of the error vector <sup>9</sup> is performed with a memory block.

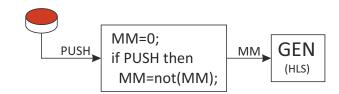

The third block holds the RMM. However, since it was also necessary to create a signal source and to upsample the RMM output in order to prepare it for filtering, all these functions were combined in just one block. So, this major block will internally generate an OQPSK signal, perform RMM on it and then upsample the resulting signal, making it ready to pass through the RRC. Due to the quantity of different operations that this block has to perform, it will just be called "Generator". A block diagram of this system is depicted in Figure 4.12.

#### **Generator block implementation**

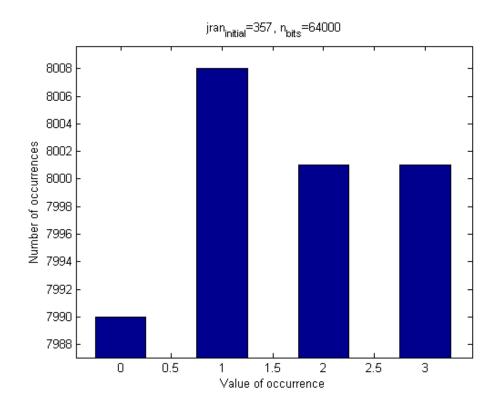

The Generator uses a fast algorithm (based on the fast C algorithms from [53], which will be discussed in detail in Chapter 5) in C to create *random*<sup>10</sup> numbers of two bits between 0 and 3, since the employed modulation is OQPSK, i.e., one bit for the in-phase part and other for the quadrature part. Next, the generated symbols enter sequentially a

<sup>&</sup>lt;sup>9</sup>Refer to Eq. 2.13.

<sup>&</sup>lt;sup>10</sup>Almost none of the random number generator (RNG) algorithms can generate "true" randomness, unless they use external random variables.

Figure 4.12: Generator block diagram.