João Leonel Almeida Amaro

# Synthetic Aperture beamforming processing on GPUs using OpenCL

Coimbra, Setembro de 2013

Universidade de Coimbra

## Synthetic Aperture beamforming processing on GPUs using OpenCL

## João Leonel Almeida Amaro

# Dissertação para obtenção do Grau de Mestre em **Engenharia Electrotécnica e de Computadores**

JúriPresidente:Doutor Jaime Batista dos SantosOrientador:Doutor Gabriel Falcão Paiva FernandesVogais:Doutor Vítor Manuel Mendes da Silva

Setembro de 2013

# Agradecimentos

Gostaria de começar por agradecer ao meu orientador, o Professor Gabriel Falção pelo seu acompanhamento constante do meu trabalho e pelo tempo dispensado a solucionar problemas e a propor ideias para melhorar o projecto. Gostaria de dar uma nota de destaque também ao João Andrade e ao Luís Oliveira, colegas de laboratório que se dispuseram a partilhar o seu conhecimento comigo nas variadas vertentes, e assim suavizar a minha curva de aprendizagem; e pela companhia proporcionada nas longas horas passadas no laboratório. Gostaria também de agradecer ao Professor Marco Gomes pelas diversas ocasiões em que interrompi o seu trabalho com dúvidas, e ele se dispôs a me auxiliar, indicando-me sempre o caminho certo a seguir. Gostaria de agradecer também a todos os meus amigos, a alguns pelo apoio proporcionado pelo facto de estarem perto, a outros pela paciência e compreensão pelo pouco tempo que aloquei para eles; por sempre terem manifestado interesse no meu trabalho, e estarem dispostos a ouvir-me explicá-lo exaustivamente. Agradeço também à minha mãe e ao meu pai, pois como família, sempre me apoiaram e aturaram, sem nunca deixar de zelar pelo meu bem-estar. Ao Diogo e ao Xico, pois como bons irmãos, me proporcionaram momentos de descontracção e humor quando chegava a casa. À minha namorada, Carina, por todo o amor e apoio que me deu durante todo este ano, muitas vezes pondo de lado os seus interesses pelos meus, e por me encorajar e disciplinar nos momentos em que a exaustão se começava a instalar. A todos vocês, não existem palavras grandes o suficiente para descrever o meu sentimento de gratidão.

## Abstract

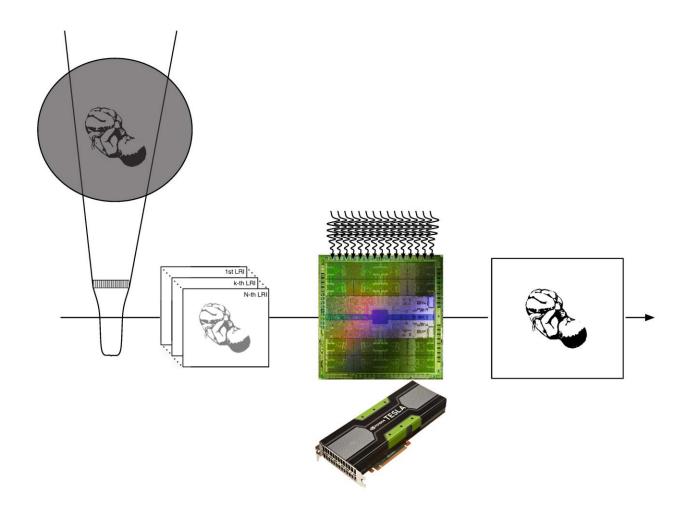

Synthetic Aperture (SA) Beamforming techniques represent the future of medical ultrasound imaging. The image quality and low number of artifacts introduced make it an optimal replacement for current B-scan pulse-echo imaging systems. Nonetheless, the computational workload introduced by such techniques is very high. This work suggests Graphics Processing Units (GPUs) as the solution to this problem, by implementing portable parallel kernels, under the Open Computing Language (OpenCL) framework, of a delay-and-sum approach of the SA beamforming technique. The GPU was the choice given its architecture, that perfectly suits parallel tasks by dividing the labour between several work-items, and therefore, its characteristics, advantages and disadvantages are discussed. The OpenCL framework allows for the use of one code in multiple devices, be it GPUs, Central Processing Units (CPUs) or even Field-Programmable Gate Arrays (FPGAs), and its workings are also examined.

# Keywords

SA, Ultrasound Imaging, OpenCL, GPU, multiple GPU, Parallel Programming

## Resumo

As técnicas de *SA Beamforming* representam o futuro da ultrasonografia. A qualidade de imagem melhorada e a baixa incidência de artefactos de imagem, fazem delas óptimas substitutas para os sistemas actuais, baseados em técnicas B-scan por recepção de eco. Ainda assim, a carga de computação introduzida por este tipo de técnicas é bastante elevada. Este trabalho surere as GPUs como uma possível solução para este problema, ao implementar kernels paralelos portáveis, sob a *framework* OpenCL, de uma aproximação *delay-and-sum* das técnicas de *SA Beamforming*. A GPU é escolhida dada a natureza da sua arquitectura, que se adequa perfeitamente a tarefas paralelas ao dividir o trabalho entre diversos *work-items*, e por conseguinte, as suas características, vantagens e desvantagens são abordadas. A *framework* OpenCL possibilita a utilização de um código em múltiplos dispositivos de computação *manycore*, tais como GPUs, CPUs ou ainda FPGAs, e a sua operação é igualmente discutida.

# **Palavras Chave**

SA, Ultrasonografia, OpenCL, GPU, múltiplas GPU, Programação Paralela

# Contents

| Intro | oductio                                                                                                                                           | 'n                                                                                                                                                                                                                                                                                                                                                    | 1                                 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 1.1   | Motiva                                                                                                                                            | ation                                                                                                                                                                                                                                                                                                                                                 | 2                                 |

| 1.2   | Object                                                                                                                                            | tives                                                                                                                                                                                                                                                                                                                                                 | 3                                 |

| 1.3   | Main c                                                                                                                                            | contributions                                                                                                                                                                                                                                                                                                                                         | 3                                 |

| 1.4   | Disser                                                                                                                                            | tation outline                                                                                                                                                                                                                                                                                                                                        | 3                                 |

| Ultr  | asound                                                                                                                                            | Theory and Imaging Algorithms                                                                                                                                                                                                                                                                                                                         | 5                                 |

| 2.1   | Theore                                                                                                                                            | etical Model                                                                                                                                                                                                                                                                                                                                          | 6                                 |

| 2.2   | System                                                                                                                                            | n Geometry and Operation Fundamentals                                                                                                                                                                                                                                                                                                                 | 6                                 |

|       | 2.2.1                                                                                                                                             | Probe Topology                                                                                                                                                                                                                                                                                                                                        | 8                                 |

|       |                                                                                                                                                   | 2.2.1.A Beamsteering                                                                                                                                                                                                                                                                                                                                  | 10                                |

|       |                                                                                                                                                   | 2.2.1.B Beamforming                                                                                                                                                                                                                                                                                                                                   | 11                                |

| 2.3   | Ultrase                                                                                                                                           | ound Wave Generation                                                                                                                                                                                                                                                                                                                                  | 12                                |

|       | 2.3.1                                                                                                                                             | Amplitude                                                                                                                                                                                                                                                                                                                                             | 12                                |

|       | 2.3.2                                                                                                                                             | Frequency and Wavelength                                                                                                                                                                                                                                                                                                                              | 13                                |

|       | 2.3.3                                                                                                                                             | Waveform                                                                                                                                                                                                                                                                                                                                              | 13                                |

| 2.4   | Beaml                                                                                                                                             | ine based Pulse-Echo Imaging (B-scan)                                                                                                                                                                                                                                                                                                                 | 14                                |

|       | 2.4.1                                                                                                                                             | Data Acquisition                                                                                                                                                                                                                                                                                                                                      | 14                                |

|       | 2.4.2                                                                                                                                             | Signal pre-processing                                                                                                                                                                                                                                                                                                                                 | 16                                |

|       |                                                                                                                                                   | 2.4.2.A Filtering                                                                                                                                                                                                                                                                                                                                     | 16                                |

|       |                                                                                                                                                   | 2.4.2.B Time-Gain Compensation (TGC)                                                                                                                                                                                                                                                                                                                  | 16                                |

|       |                                                                                                                                                   | 2.4.2.C Analog to Digital (A/D) conversion and Envelope Ex-                                                                                                                                                                                                                                                                                           |                                   |

|       |                                                                                                                                                   | traction                                                                                                                                                                                                                                                                                                                                              | 16                                |

| 2.5   | SA Be                                                                                                                                             | amforming Imaging                                                                                                                                                                                                                                                                                                                                     | 17                                |

|       | 2.5.1                                                                                                                                             | Data Acquisition                                                                                                                                                                                                                                                                                                                                      | 18                                |

|       | 2.5.2                                                                                                                                             | Signal Processing                                                                                                                                                                                                                                                                                                                                     | 18                                |

|       | 2.5.3                                                                                                                                             | LRI Formation                                                                                                                                                                                                                                                                                                                                         | 19                                |

|       | 2.5.4                                                                                                                                             | HRI Compounding                                                                                                                                                                                                                                                                                                                                       | 20                                |

| 2.6   | SA Be                                                                                                                                             | camforming vs. B-scan techniques                                                                                                                                                                                                                                                                                                                      | 21                                |

|       | <ol> <li>1.1</li> <li>1.2</li> <li>1.3</li> <li>1.4</li> <li>Ultrazon</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> </ol> | <ol> <li>1.1 Motiva</li> <li>1.2 Object</li> <li>1.3 Main of</li> <li>1.4 Disser</li> <li>Ultrasound</li> <li>2.1 Theore</li> <li>2.2 System</li> <li>2.2.1</li> <li>2.3 Ultraso</li> <li>2.3.1</li> <li>2.3.2</li> <li>2.3.3</li> <li>2.4 Beaml</li> <li>2.4.1</li> <li>2.4.2</li> <li>2.5.1</li> <li>2.5.2</li> <li>2.5.3</li> <li>2.5.4</li> </ol> | <ul> <li>1.2 Objectives</li></ul> |

|   | 2.7  | Conclu    | usions                                                | 21 |

|---|------|-----------|-------------------------------------------------------|----|

| 3 | Para | allel Co  | mputing Frameworks and Manycore Devices               | 23 |

|   | 3.1  | The O     | penCL Parallel Programming Model                      | 24 |

|   |      | 3.1.1     | Platform Model                                        | 24 |

|   |      | 3.1.2     | Runtime Model                                         | 25 |

|   |      |           | 3.1.2.A Command-queues                                | 26 |

|   |      |           | 3.1.2.B Memory Model and Allocation                   | 26 |

|   |      |           | 3.1.2.C Kernel Work Size and Execution                | 28 |

|   |      |           | 3.1.2.D Optimization Strategies                       | 28 |

|   | 3.2  | The m     | ulticore CPU                                          | 30 |

|   |      | 3.2.1     | Control Unit                                          | 31 |

|   |      | 3.2.2     | Arithmetic and Logic Unit (ALU)                       | 31 |

|   |      | 3.2.3     | Memory Interface and Caches                           | 32 |

|   |      |           | 3.2.3.A Dynamic Random Access Memory (DRAM) and Read  |    |

|   |      |           | Only Memory (ROM)                                     | 32 |

|   |      |           | 3.2.3.B Caches                                        | 33 |

|   | 3.3  | The m     | anycore GPU                                           | 34 |

|   |      | 3.3.1     | Streaming Processors (SPs)                            | 34 |

|   |      | 3.3.2     | Memory-Hierarchy                                      | 35 |

|   |      | 3.3.3     | Mapping the GPUs Memory Regions to the OpenCL Address |    |

|   |      |           | Spaces                                                | 38 |

|   | 3.4  | Conclu    | usion                                                 | 39 |

| 4 | Para | allel Syr | nthetic Aperture Beamforming on Manycore Devices      | 41 |

|   | 4.1  | Outlin    | ing                                                   | 42 |

|   |      | 4.1.1     | SA Beamforming Kernels                                | 42 |

|   |      | 4.1.2     | Simulation Apparatus                                  | 46 |

|   |      | 4.1.3     | Performance Metrics                                   | 47 |

|   |      |           | 4.1.3.A Throughput and Overall processing Time        | 48 |

|   |      |           | 4.1.3.B Memory Transfer Rates (Average and Slowest)   | 48 |

|   |      |           | 4.1.3.C Kernel Occupancy                              | 48 |

|   | 4.2  | Experi    | imental Results                                       | 48 |

|   |      | 4.2.1     | Single GPU scenario                                   | 48 |

|   |      |           | 4.2.1.A Advanced Micro Devices (AMD)                  | 49 |

|   |      |           | 4.2.1.B NVIDIA                                        | 49 |

|   |      | 4.2.2     | Multiple GPUs scenario                                | 49 |

|   |      |           | 4.2.2.A Dual AMD                                      | 49 |

| A | Арр | endix A          |                   | 59 |

|---|-----|------------------|-------------------|----|

|   | 5.1 | Future Work      |                   | 56 |

| 5 | Con | clusions         |                   | 55 |

|   | 4.4 | Conclusions      |                   | 54 |

|   | 4.3 | Analyzing the ob | tained results    | 50 |

|   |     | 4.2.2.C          | Hybrid AMD/NVIDIA | 50 |

|   |     | 4.2.2.B          | Dual NVIDIA       | 50 |

Contents

# **List of Figures**

| 2.1  | Single transducer lying on the x-axis, and Region of Interest (ROI) in the |    |

|------|----------------------------------------------------------------------------|----|

|      | x-z plane                                                                  | 7  |

| 2.2  | Single transducer operating in active mode, with echoes occurring in the   |    |

|      | scattering points of the medium.                                           | 7  |

| 2.3  | Single transducer operating in passive mode, receiving the echoes, and     |    |

|      | outputting an electrical signal.                                           | 8  |

| 2.4  | Array of transducers operating in active mode, and arbitrary point $R$     | 9  |

| 2.5  | Array of transducers performing lateral steering                           | 10 |

| 2.6  | Array of transducers performing angular steering                           | 10 |

| 2.7  | Example of beamforming for three different scenarios. [1, pp. 183]         | 11 |

| 2.8  | Gaussian modulated sinusoidal pulse waveform                               | 14 |

| 2.9  | Basic B-scan Geometry                                                      | 15 |

| 2.10 | Typical wave transmission/reception in SA Beamforming                      | 18 |

| 2.11 | Hilbert FIR filter design.                                                 | 19 |

| 3.1  | OpenCL Device Query.                                                       | 25 |

| 3.2  | OpenCL Queue Creation.                                                     | 26 |

| 3.3  | OpenCL Buffer Creation and Mapping/Enqueuing.                              | 27 |

| 3.4  | OpenCL Address Space. [2]                                                  | 27 |

| 3.5  | OpenCL Kernel Execution/Memory Operations Overlapping. [3]                 | 29 |

| 3.6  | Intel Haswell architecture die. [4]                                        | 30 |

| 3.7  | AMD Piledriver architecture die. [5]                                       | 31 |

| 3.8  | Current generation quadcore CPU basic diagram. Intel and AMD CPUs          |    |

|      | differences are highlighted.                                               | 32 |

| 3.9  | Random Access Memory (RAM) stick from Corsair. [6]                         | 33 |

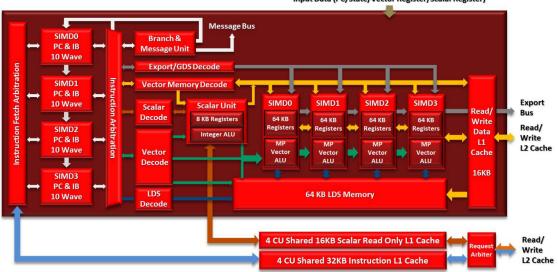

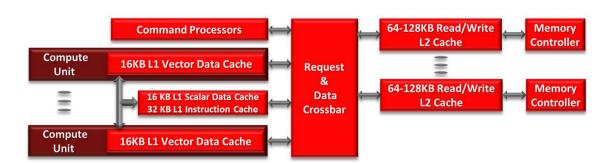

| 3.10 | GCN Compute Unit Architecture. [7]                                         | 35 |

|      | GCN Basic Memory Model. [7]                                                | 36 |

|      | Kepler Stream Multiprocessor (SMX) model. [8]                              | 37 |

|      |                                                                            |    |

| 3.13 | Kepler Generic Architecture. [8]                                           | 38 |

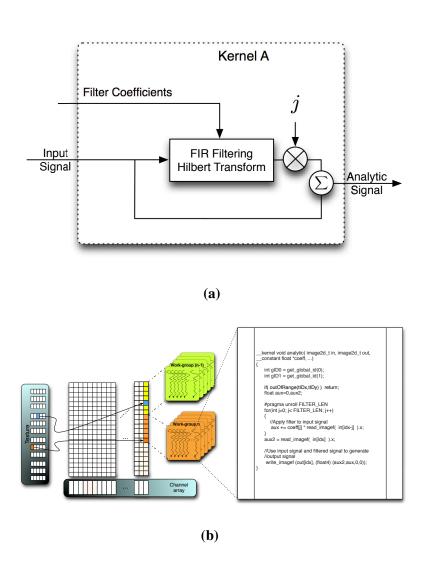

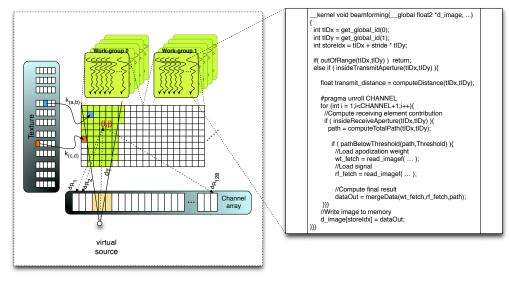

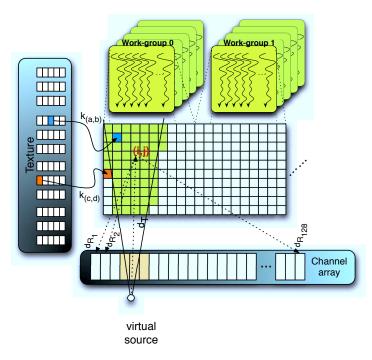

| 4.1 | Kernel A block diagram and algorithm structure on the GPU                    | 43 |

|-----|------------------------------------------------------------------------------|----|

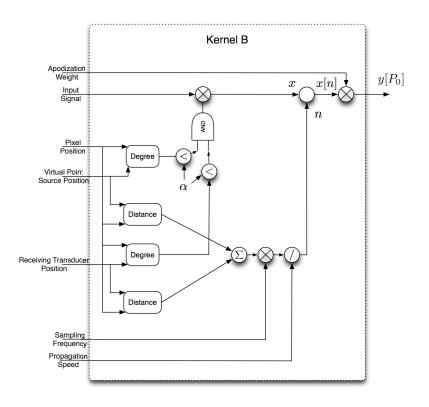

| 4.2 | Kernel B block diagram and algorithm structure on the GPU                    | 44 |

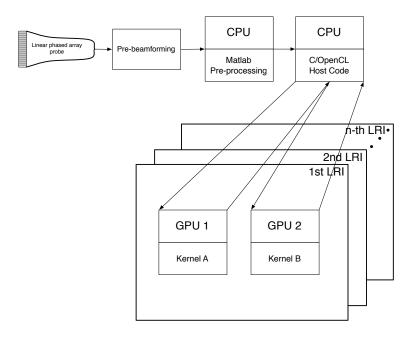

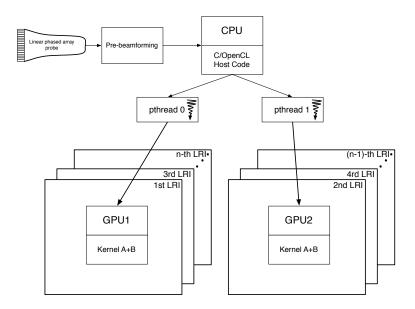

| 4.3 | Structural outline of the two parallel approaches followed in this work      | 45 |

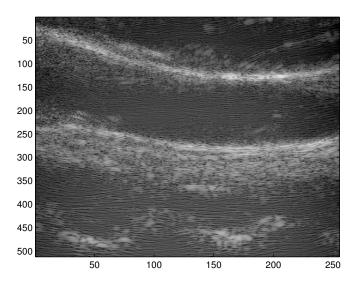

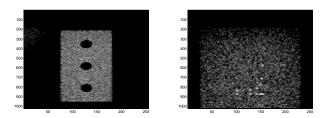

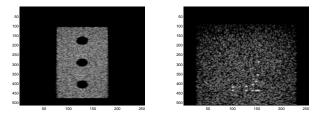

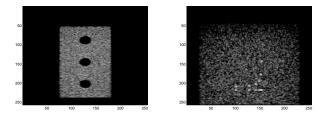

| 4.4 | Reconstructed image of an in-vivo carotid, computed in the simulations       | 47 |

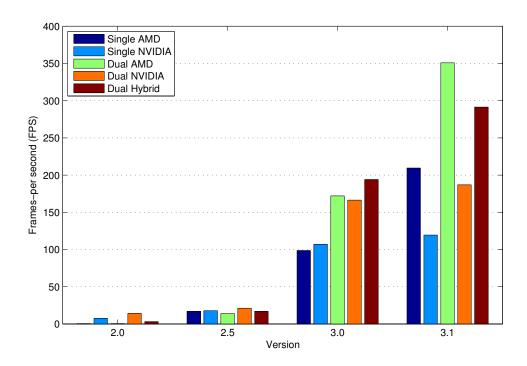

| 4.5 | Throughput comparison between the different scenarios and versions           | 51 |

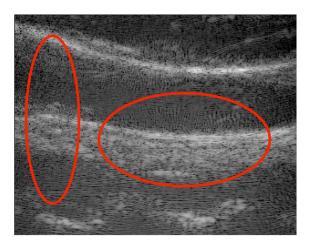

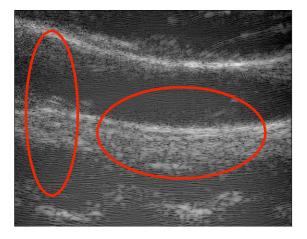

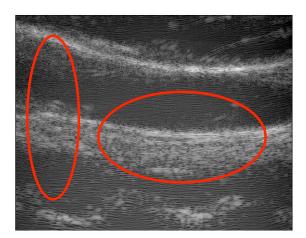

| 4.6 | Images reconstructed with various lateral resolutions to evaluate its effect |    |

|     | on image quality. Highlighted in red are the regions where the differences   |    |

|     | can be seen. In subfigures b) and c), the incidence of image artifacts is    |    |

|     | much lower than that of subfigure a), which has lower lateral resolution.    | 53 |

# **List of Tables**

| 4.1 | Host Platform Specs.                         | 47 |

|-----|----------------------------------------------|----|

| 4.2 | Results for the single AMD scenario          | 49 |

| 4.3 | Results for the single NVIDIA scenario       | 49 |

| 4.4 | Results for the dual AMD scenario.           | 50 |

| 4.5 | Results for the dual NVIDIA scenario         | 50 |

| 4.6 | Results for the multiple hybrid GPU scenario | 51 |

# **List of Algorithms**

# **List of Acronyms**

| A/D  | Analog to Digital                   |

|------|-------------------------------------|

| ALU  | Arithmetic and Logic Unit           |

| AMD  | Advanced Micro Devices              |

| ΑΡΙ  | Application Programming Interface   |

| BU   | Branch Unit                         |

| CPU  | Central Processing Unit             |

| CU   | Compute Unit                        |

| CUDA | Compute Unified Device Architecture |

| DRAM | Dynamic Random Access Memory        |

| DSP  | Digital Signal Processor            |

| FIR  | Finite Impulse Response             |

| FPGA | Field-Programmable Gate Array       |

| FPS  | frames-per-second                   |

| FSB  | Front-Side Bus                      |

| GCN  | Graphic Core Next                   |

| GPR  | General-Purpose Register            |

| GPU  | Graphics Processing Unit            |

| HRI  | High-Resolution Image               |

| LDS  | Local Data Shared Memory            |

| LRI    | Low-Resolution Image                      |

|--------|-------------------------------------------|

| MTR    | Memory Transfer Rate                      |

| N/A    | Non-Applicable                            |

| NDE    | Non-Destructive Evaluation                |

| OpenCL | Open Computing Language                   |

| OS     | Operating System                          |

| PCle   | Peripheral Component Interconnect Express |

| RAM    | Random Access Memory                      |

| ROI    | Region of Interest                        |

| ROM    | Read Only Memory                          |

| SA     | Synthetic Aperture                        |

| SDK    | Software Development Kit                  |

| SFU    | Special Function Unit                     |

| SMX    | Stream Multiprocessor                     |

| SP     | Streaming Processor                       |

| SIMD   | Single Instruction Multiple Data          |

| SIMT   | Single Instruction Multiple Thread        |

| SNR    | Signal-to-Noise Ratio                     |

| SRAM   | Static Random Access Memory               |

| TGC    | Time-Gain Compensation                    |

| ТР     | Thread Processor                          |

| VLIW   | Very Long Instruction Word                |

|        |                                           |

#

# Introduction

## Contents

| 1.1 | Motivation           |  |

|-----|----------------------|--|

| 1.2 | <b>Objectives</b>    |  |

| 1.3 | Main contributions   |  |

| 1.4 | Dissertation outline |  |

#### 1. Introduction

Since the inception of the medical imaging field, the ultrasonography has been shown to be a utmost useful tool. Its applications range from diagnosis to the control of biological processes such as pregnancies, ovary cysts, vascular structures' blood flow, and also operates as a guiding system in certain types of biopsies and other surgical procedures. Because of its application range, ultrasound systems are widely used, but they require the use of large amounts of very complex hardware, such as Digital Signal Processors (DSPs) and arrays of Field-Programmable Gate Arrays (FPGAs). The complexity resides not only in its physical nature, but also in the way they are programmed to perform the desired task. On top of that, if we consider, for example FPGAs, they represent significant costs, which means that current ultrasound systems have ample space for improvement, in every way. The maintenance of such devices is not trivial, and can represent additional costs.

## **1.1 Motivation**

In medical imaging, the most common ultrasound technology is the beamline based B-scan, a technique that displays a 2-D image of the Region of Interest (ROI). To do so, it is required to perform a full sweep of the entire array of transducers in order to be able of generating a single image. Additionally, since the transmitted wave is a beamline, it is very common to obtain image artefacts, a highly negative aspect, considering the sensitive nature associated with medical imaging.

Alternatively, Synthetic Aperture (SA) Beamforming (a technique developed in the 1950s, but only in recent years being used for medical applications) emulates a spherical wave by performing a relative delay transmission of several of the transducers, minimizing image artefacts. A given image is the compounding of a full sweep of the transducer array. To obtain a new image, only a new firing is required, thus addressing the ultra-high frame-rate issue. Of course, the computational workload brought on by this technique is several times higher than that of the conventional beamline method, which represents a significant problem. As previously stated, the computational workload is already an undesirable aspect of current systems because of the required hardware resources to perform the imaging.

There are currently two frameworks that allow the programmer to program parallel tasks to be implemented on Graphics Processing Units (GPUs): the Compute Unified Device Architecture (CUDA) and Open Computing Language (OpenCL). The former is only compatible with NVIDIA GPUs, although it is highly optimized for these architectures. OpenCL is an open standard, meaning all the major brands include in their GPUs support for this Application Programming Interface (API). As an added functionality, Central

Processing Units (CPUs), DSPs and other types of computing devices nowadays support OpenCL. The downside to this interoperability is that OpenCL was not designed towards a specific architecture, meaning a certain task in OpenCL will most likely come second to CUDA, in terms of performance. To compensate this, the manufacturers have been developing architecture-oriented functionalities that leverage the performance to peaks similar to those obtained with CUDA (then again, sacrificing the interoperability of OpenCL code).

## 1.2 Objectives

The core of this thesis work is to take advantage of this parallel processing potential to implement a time-domain version of the SA Beamforming imaging algorithm, using GPUs and CPUs under the C++ OpenCL API for parallel applications. The final goal consists of proving the feasibility of a medical ultrasound imaging system with increased portability, achieving ultra-high frame-rates and improved image quality than current systems, while using GPUs and CPUs; ubiquitous devices one might find in its very own computer.

## **1.3** Main contributions

To enhance current medical ultrasound imaging systems, massive computing power is required. Therefore, GPUs and CPU are proposed in this work, and they show it is possible to achieve portability over different many-core systems, that are capable of running OpenCL kernels. The system provides real-time capability, achieving near 350 framesper-second (FPS), and it also features adaptability to the hardware characteristics, ensuring proper performance.

## **1.4 Dissertation outline**

This thesis is structured in five chapters. Following the introduction, Chapter 2 will focus on the basic principles of ultrasound imaging, particularly in medical applications, as well as the signal processing involved in the SA beamforming method. In chapter 3, GPU architecture will be discussed, followed by an explanation of the workings of the OpenCL framework. Chapter 4 will feature the experimental results obtained along the work developed. Finally, in Chapter 5, we will discuss the conclusions of this work, while also providing a path for future work in this field.

## 1. Introduction

# Ultrasound Theory and Imaging Algorithms

| C | on | teı | nts |

|---|----|-----|-----|

|   |    |     |     |

| 2.1 | Theoretical Model    6                         |

|-----|------------------------------------------------|

| 2.2 | System Geometry and Operation Fundamentals     |

| 2.3 | Ultrasound Wave Generation                     |

| 2.4 | Beamline based Pulse-Echo Imaging (B-scan)     |

| 2.5 | Synthetic Aperture (SA) Beamforming Imaging 17 |

| 2.6 | SA Beamforming vs. B-scan techniques           |

| 2.7 | Conclusions                                    |

This chapter discusses the basic principles that serve as foundation for ultrasound imaging in medical applications, in general. Nonetheless, the reader is expected to have a certain knowledge of wave propagation and signal processing theory. If that's not the case, the reader can refer itself to [9] [1]

SA Beamforming and Beamline-based B-scan methods are exploited in more detail, the former due to its relevance regarding this thesis, the latter as a term of comparison against the first, and for currently being the most common choice in medical ultrasound imaging systems.

## 2.1 Theoretical Model

Since ultrasound imaging is modelled by wave propagation theory, it is important to establish the particular conditions that describe the problem. Radar and Sonar ultrasound imaging evaluate distant objects that lie in the Fraunhofer region, or Far-field, as opposed to Non-Destructive Evaluation (NDE) and medical ultrasound imaging, whose ROI mainly lie on the Fresnel Region, or Near-field [10, pp. 413].

## 2.2 System Geometry and Operation Fundamentals

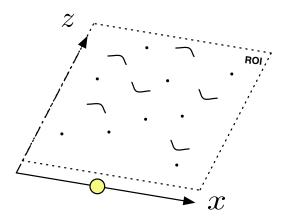

In ultrasound imaging, transducers are used to transmit acoustic signals, and also to receive the reflections generated by discontinuities in the medium. An acoustic wave is called an ultrasound wave when its frequency is high enough such that the wave is above the human audible range. Usually, this threshold varies from person to person, but it's located around 20kHz [1]. This chapter has the purpose of conveying the reader with a basic knowledge of the fundamentals of ultrasound imaging, particularly beamline based B-scan and medical SA beamforming. Let's consider the scenario represented in Fig 2.1:

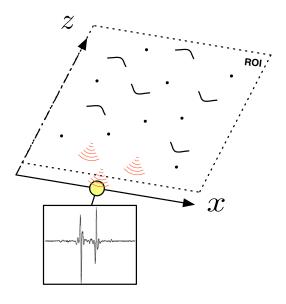

Figure 2.1: Single transducer lying on the x-axis, and ROI in the x-z plane.

A single circular electro-acoustic transducer, to which we can refer as aperture [AFT] positioned along the x-axis is evaluating a ROI placed in the x-z plane. When the transducer is in active mode, it is excited by an electrical impulse, causing it to transmit an acoustic wave into the ROI, as seen of Fig 2.2. This acoustic wave propagates through the medium, and when a discontinuity is hit, the structures have different acoustic impedances. This, of course, means that the discontinuity is also characterized by a reflection coefficient, and that wave reflections will occur in this point.

Figure 2.2: Single transducer operating in active mode, with echoes occurring in the scattering points of the medium.

When operating in passive mode, the transducer can be viewed as a receiver, which is to say, given a received echo, the transducer will generate an electrical signal, whose amplitude will depend on the amplitude and frequency of the acoustic signal.

Figure 2.3: Single transducer operating in passive mode, receiving the echoes, and outputting an electrical signal.

#### 2.2.1 Probe Topology

In medical ultrasound imaging, there are many probe topologies. On the course of this work, the preferred topology is the linear transducer phased array. This topology allows for a number of techniques, such as beamsteering and beamforming, that endow the system with more powerful information [1, pp.173-181].

Still considering the scenario described by Fig. 2.1, and given the fact that the wave is acoustic, its effect in the field manifests itself in the form of a pressure.

Using the Huygens principle, that states that every point in a wavefront is a source of wavelets [11, pp. 412], and if the condition defined in equation 2.1 is met, we can treat the aperture, whose diameter is represented by a, as a circular diffraction slit. In this specific case, this aperture corresponds to the transducer surface.

$$a < \lambda, \tag{2.1}$$

$\lambda$  representing the wavelength of the transmitted wave.

The pressure generated due to the acoustic perturbation induced by the source (the transducer) in the arbitrary point R can therefore be calculated by:

$$P(x,z) = \iint_{surface} A_0(x_0, z_0) \frac{e^{j(wt - kd(x_0, z_0, x, z) + \varphi(x_0, z_0))}}{d(x_0, z_0, x, z)} ds,$$

(2.2)

where  $A_0(x_0, z_0)$  and  $\varphi(x_0, z_0)$  represent the reference amplitude and phase of the infinitesimal field source point located at coordinates  $(x_0, z_0)$ ,  $d(x_0, z_0, x, z)$  is the distance between the source point and R, and k is the wave number.

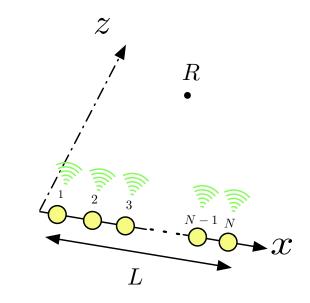

To compute the pressure at an arbitrary point R due to the perturbation caused by an array of transducers (see Fig 2.4) with length L comprised of N individual transducers, the superposition theorem is employed [1, pp. 173], and equation 2.2 becomes:

$$P(x,z) = \sum_{i \text{ surface}-i}^{N} \iint_{a_{0i}(x_{0},z_{0})} \frac{e^{j(wt-kd(x_{0},z_{0},x,z)+\varphi_{i}(x_{0},z_{0}))}}{d(x_{0},z_{0},x,z)} ds_{i}.$$

(2.3)

Figure 2.4: Array of transducers operating in active mode, and arbitrary point R.

The position of each transducer,  $x_i$ , is given by:

$$x_i = (i-1) \times \Delta_x - \frac{L}{2}.$$

(2.4)

The dimensions and spacing of the transducers (represented by  $\Delta_x$  in Eq. 2.4) are of critical importance, as an incorrect design will give way to catastrophic results, with the appearance of grating lobes in the radiation pattern [1, pp. 175]. The condition to prevent this undesired phenomenon is:

$$\Delta x \le \lambda. \tag{2.5}$$

To conclude this section, we establish that the system will operate in *strip-map mode*, as the ROI will be swept along the *x*-axis, and the reconstructed image will be shaped like

a "strip".

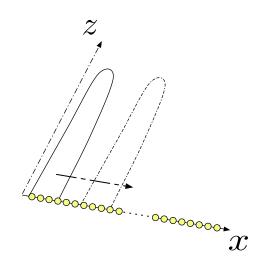

#### 2.2.1.A Beamsteering

Beamsteering is the process of electronically change the radiation pattern of an antenna, in this case, of the array. The simplest way of achieving this is to perform lateral steering, where in the *i*-th firing, transducers  $i \times n$  to  $i \times n + m$  are used in the transmission, whereas in the *i*+1-th firing, the transmitting transducers are  $(i + 1) \times n$  to  $(i+1) \times n + m$  [1, pp. 176]. This process is represented in Fig. 2.5.

Figure 2.5: Array of transducers performing lateral steering.

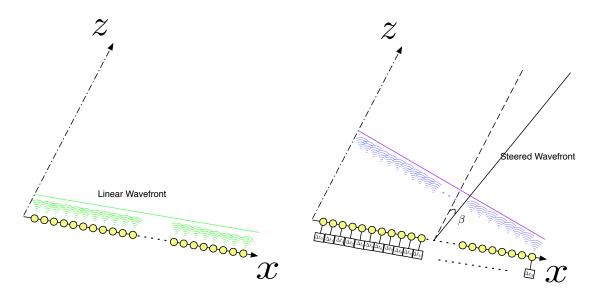

Another common type of beamsteering is the angular steering:

Figure 2.6: Array of transducers performing angular steering.

Until now, we have only considered beams perpendicular to the array of transducers, but through angular steering, it is possible to tilt the transmission, even if only up to a certain angle. This is possible by introducing relative delays to each transducer element, so that the waves from each transducer element reach the dotted line in Fig. 2.6 at the same time [1, pp. 178]. Taking equation 2.4, the expression for each transducers' relative delay is:

$$\Delta_i = [(i-1) \times \Delta x - \frac{L}{2}] \times \frac{\sin(\beta)}{v_p}, \qquad (2.6)$$

where  $\beta$  corresponds to the angle between the *z*-axis and the direction of propagation of the wavefront. This angle is limited, under penalty of appearing grating lobes. Therefore, in addition to equation 2.5, the design of the system must also obey:

$$\beta_{max} = \sin^{-1}(\frac{\lambda}{\Delta x} - 1). \tag{2.7}$$

#### 2.2.1.B Beamforming

By combining the aforementioned methods of beamsteering and by shaping the acoustic beam, we arrive at a process called beamforming, whose main advantage is that of achieving beam focusing [1, pp. 182]. Consider a new arbitrary point over the *z*-axis, lying at a distance *F* from the axis' origin. The pulse (traveling with a propagation speed of  $v_p$ ) emitted from the central transducer will reach the focal point after:

$$\Delta t = \frac{F}{v_p}.$$

(a)  $\beta = -10^{\circ}; F = 80$ mm

**(b)**  $\beta = 0^{\circ}; F = 50 \text{mm}$

(c)  $\beta = 20^{\circ}; F = 90$ mm

Figure 2.7: Example of beamforming for three different scenarios. [1, pp. 183]

(2.8)

#### 2. Ultrasound Theory and Imaging Algorithms

Fig. 2.7 represents three different scenarios where the beam is angled with different degrees  $\beta$ , and whose focal point lies at different distances *F*.

To achieve focusing, the pulses emitted by all the transducers must reach the focal point at the same time. With  $x_i$  representing the position of the *i*-th transducer:

$$\frac{\sqrt{x_i^2 + F^2}}{v_p} = \frac{F}{v_p},$$

(2.9)

which yields:

$$\Delta t_i = \frac{F - \sqrt{x_i^2 + F^2}}{v_p},$$

(2.10)

where  $\Delta t_i$  stands for the relative time delay of the *i*-th transducer. It is possible that equation 2.10 outputs a negative time delay. In such event, the solution is to simply shift the reference transducer to that whose distance to the focal point is shorter (alternatively, the one with the most negative time delay).

Finally, to achieve beamforming, it is necessary to combine the focusing effect described above with the lateral and angular steering concepts. This is achieved by combining Equations 2.10 and 2.6.

## 2.3 Ultrasound Wave Generation

Acoustic transducer elements are composed of a group piezoelectrical crystals, that vibrate when subjected to an electric current. This vibration generates an acoustic wave [1]. This wave can be characterized by its amplitude, waveform, frequency and wavelength. To choose a pulse for transmission, it is important to first understand how each of these characteristics affect the global performance of the system.

### 2.3.1 Amplitude

Depending on the characteristics of the input signal, the amplitude of the acoustic wave can vary. The maximum achievable amplitude is limited by the piezoelectric crystals. The intensity of a wave is directly proportional to the square of the amplitude. When the intensity of a propagating wave is high, non-linear effects such as the appearance of harmonic waves start to appear.

#### 2.3.2 Frequency and Wavelength

Frequency and wavelength are interdependent, since one can be obtained from the other by the following relation:

$$\lambda = \frac{v_p}{f},\tag{2.11}$$

where f is the frequency in Hz,  $\lambda$  represents the wavelength in meters and  $v_p$  corresponds to the propagation speed, in m/s.

The frequency of the transmitted pulse directly affects the spatial resolution of the reconstructed image. On the other hand, when the frequency is raised, so is the attenuation, defined by the absorption of a part of the wave's energy by the medium, and also dependent on the distance covered by the wave. The following equations give a simplified view of the total attenuation:

$$\alpha_c = \alpha_0 + \alpha_1 f^y, \qquad (2.12)$$

$$A(x,f) = \alpha_c(f) \times r, \qquad (2.13)$$

with x representing the distance from the transducer,  $\alpha_c$  representing the attenuation coefficient and  $\alpha_0$  and  $\alpha_1$  are constants depending on the physical parameters of the medium. Given the fact that in medical imaging, the ROI is mainly comprised of soft tissues, it is assumed that y = 1 and thus, the relation between the attenuation coefficient and the frequency is linear. In different scenarios, y can assume any value between 1 and 2, depending on the nature of the tissues under evaluation.

This puts the choice of the frequency of operation into a new perspective, since higher frequencies will yield lower distances of penetration, but better resolution, so high frequencies are most suited for the evaluation of superficial tissue. On the contrary, lower frequencies, while achieving lower spatial resolutions, can travel a greater distance, and are best suited for the appraisal of deeper structures [12].

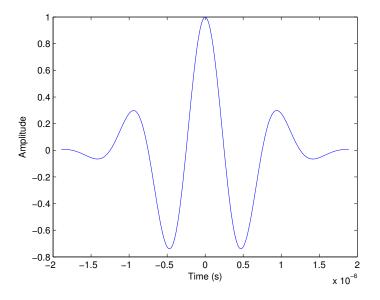

#### 2.3.3 Waveform

The nature of medical applications of ultrasound imaging dictate the requirement for short, time-domain wise, pulses, or broadband pulses. Although there are many possibilities that fulfil these needs, it is very common to use the Gaussian modulated sinusoidal pulse [1, pp. 99] [13], as seen in Fig. 2.8, and defined by:

$$g(t) = e^{-\beta t^2} \cos 2\pi f_c t,$$

(2.14)

where  $f_c$  stands for the center frequency of the pulse, and  $\beta$  represents its width.

Figure 2.8: Gaussian modulated sinusoidal pulse waveform.

## 2.4 Beamline based Pulse-Echo Imaging (B-scan)

The B-scan is widely used throughout the world, gathering recognition as the most common method of medical ultrasound imaging method.

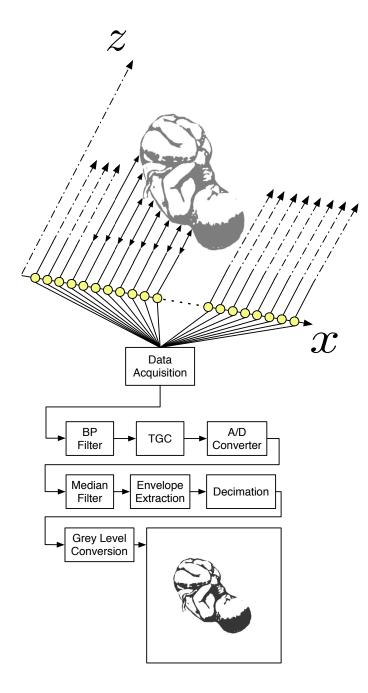

#### 2.4.1 Data Acquisition

Pulse-Echo Imaging systems are based on the transmission of a broadband pulse into the medium, and the the reception of the echoes, either by the transmitting transducers or a set of transducers exclusively dedicated to signal reception. These echoes are originated by the transmitted signal traversing discontinuities in the medium, so that the difference in the acoustic impedance and consequent reflection coefficient, provide that a fraction of the signal energy is reflected. This reflection is an angle-related function, and thus, the echo propagates in different directions. Current B-scan imaging systems already perform transmit beamforming, so unlike primordial systems, where only echoes travelling along the beamline were used, current systems provide much accurate information [14, pp. 93]. Each receiving transducer will sample one A-line, and the final image is reconstructed from the A-lines from every receiving transducer of the array. After this data acquisition step, the signal must endure a signal processing routine before it displays the reconstructed image.

Figure 2.9: Basic B-scan Geometry.

#### 2.4.2 Signal pre-processing

#### 2.4.2.A Filtering

The signal acquired by the receiving transducers includes not only the desired echoes, but also undesired noise. Consequently, this signal must undergo filtering, to eliminate as much as possible the noise (there are many sources to this noise, but in the scope of this work, they are irrelevant). The first step is high-pass filtering, since the frequency of operation is in the order of MHz, and lower frequencies carry no information. Before the Analog to Digital (A/D) conversion can take place, low-pass filtering must also be applied to the signal, mainly to limit the maximum frequency to the Nyquist frequency (otherwise, the A/D conversion would cause aliasing of the signal). These two filtering steps could also be grouped in one filter, a band-pass filter [1, pp. 208].

#### 2.4.2.B Time-Gain Compensation (TGC)

Due to the effects of attenuation, the amplitude of the signal that reaches deeper structures is significantly lower when compared to more superficial tissue. The following assumptions are made:

-The propagation speed,  $v_p$ , remains constant throughout the medium.

-The reflectivity of the scatterers is relatively equal for all the ROI.

-The attenuation coefficient,  $\alpha_c(f)$ , is also constant. This assumption is accepted if there are no bones or air in the acoustic path.

Thus, a gain factor is applied to the signal to mitigate the effects of the attenuation in the reconstructed image, and guarantee that equal structures at different depths appear the same, in the end of the image reconstruction. This process is denominated TGC [1, pp. 205].

#### 2.4.2.C A/D conversion and Envelope Extraction

The signal is now digitized and passes through a median filter, to smooth out any isolated peaks. In an imaging system, only the changes in texture represent useful information, and additional information, such as the representation of the pulse's waveform is dispensable, so the next step is to extract the signal's envelope,  $\zeta(t)$  [1, pp. 208]. To achieve this, the Hilbert transform, whose operator is represented by H{}. The frequency response of the Hilbert transform is given by:

$$H(j\omega) = -j \times sign(\omega). \tag{2.15}$$

As can be seen from Eq. 2.15, the Hilbert transform shifts all the negative frequencies by 90°, and all the positive frequencies by  $-90^{\circ}$ . The following equation is the next step in the process. The resulting signal  $\hat{S}(t)$  is known as the "analytic representation" of the signal S(t). Its properties are object of discussion in [15].

$$\hat{S}(t) = S(t) + j \times H\{S(t)\},$$

(2.16)

$$\boldsymbol{\zeta}(t) = |\hat{\boldsymbol{S}}(t)|. \tag{2.17}$$

Finally, the envelope of the original signal S(t) is extracted by computing the absolute value of  $\hat{S}(t)$ .

Since the acquired signal was a function of time, decimation is required to migrate from a time scale to a distance scale. Finally, defining a vector of N grey levels, whose minimum and maximum are  $G_{min}$  and  $G_{max}$ , respectively, the signal is quantized, by using the following relation:

$$\vec{\zeta}(t) = \begin{cases}

G_{min} , \text{ if } \zeta(t) < G_{min} \\

G_{max} , \text{ if } \zeta(t) > G_{max} \\

\text{round}(N \times \frac{\zeta(t) - G_{min}}{G_{max} - G_{min}}) , \text{ otherwise}

\end{cases}$$

(2.18)

# 2.5 SA Beamforming Imaging

SA Beamforming Imaging is a method of performing ultrasound imaging that, unlike other methods, such as the one described in the previous section, take advantage of the additional information provided by the echoes' phase, being recognized as a coherent method [14, pp. 3].

Aside from receive beamforming, this method also performs transmit beamforming. To achieve this, during the process of constructing an image, reconstructed images of subregions of the ROI, also known as a Low-Resolution Image (LRI), are also computed, and then compounded into an High-Resolution Image (HRI) [16].

There are several imaging reconstruction algorithms, but the scope of this thesis' work will only broach the Delay-and-Sum procedure.

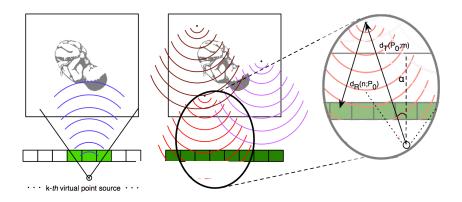

# 2.5.1 Data Acquisition

In SA Beamforming Imaging, the way data acquisition is performed differs from the one discussed in Sec. 2.4.

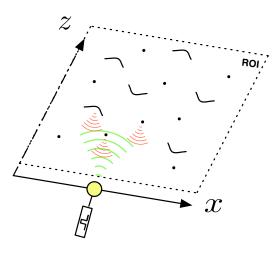

On the *m*-th firing, a set of transducers ranging from *m* to m + M will emulate the transmission of a spherical wave, as displayed in the following figure:

Figure 2.10: Typical wave transmission/reception in SA Beamforming.

When the ROI is illuminated, as discussed in the previous sections, discontinuities in the acoustic impedance, characterized by scattering structures, such as tissues, different cells, organs, etc., part of the wave's energy will be reflected. The echo's are then sampled by the entire (or just part) of the array of transducers, and then processed.

# 2.5.2 Signal Processing

After the data acquisition is completed, similarly to the Pulse-Echo technique, the signal is passed through two filtering steps, to minimize noise and consequently increase the Signal-to-Noise Ratio (SNR), then TGC is applied and the signal suffers A/D conversion. The following step again requires the transforming of the signal using the Hilbert transform. As can be seen from Eq. 2.16, the resulting signal is a complex one, and further exploring its spectral frequency, it is obvious that the original content is preserved. Furthermore, this signal includes phase information of the original data, making it a useful tool, signal processing-wise [17] [18]. Since the main focus of this thesis focuses over SA beamforming techniques, it is also important to shed some light over how the analytic representation was calculated. Eq. 2.15 provides insight over the frequency response of the Hilbert Transform. To apply this transform without crossing over to the frequencydomain, the signal was convolved with a Finite Impulse Response (FIR) filter with L taps, whose impulse response is given by:

$$h[l] = \begin{cases} 0 & \text{, for even}l\\ \frac{2}{\pi \times l} & \text{, for odd}l \end{cases}$$

(2.19)

The FIR filter coefficients were obtained using the least-square method, that approximates the frequency response of the desired filter, by minimizing the error between the ideal response and the approximated one. This was performed in Matlab, using the following commands:

```

d = fdesign.hilbert(100,0.1); %(1st argument is the order of the filter

%2nd represents the width of the transition band)

designmethods(d);

hd = design(d, 'firls');

hilbertCoeff = hd.Numerator;

```

$$a_{n,m}[g] = \sum_{l=1}^{L} h[l] \times x_{n,m}[g-l], \qquad (2.20)$$

In Eq. 2.20, *a* represents the result of the FIR filtering operation, and *x* the acquired discrete signal.

# 2.5.3 LRI Formation

After the analytic data samples are computed, the time scale is mapped into a physical scale.

The requirements to perform such task include computing, the following quantities are defined [17]

$$\tau_{n,m}[P_0] = \frac{d_T(P_0;m) + d_R(P_0;n)}{v_p},$$

(2.21)

where  $\tau_{n,m}$  represents the focusing delay from the *m*-th firing to the *n*-th receiving transducer,  $P_0$  refers to the pixel for which the focusing delay is being calculated.  $d_T(P_0;m)$  stands for the distance between virtual source point *m* and pixel  $P_0$ .  $d_R(P_0;n)$ represents the distance between said pixel and the *n*-th receiving transducer. Fig. 2.10 also illustrates this concept.

The focusing delay allows us to calculate other two quantities required to perform the scale migration:

$$k = \lfloor f_s \tau_{n,m}[P_0] \rfloor, \tag{2.22}$$

$$\chi = 1 + k - f_s \tau_{n,m} [P_0]. \tag{2.23}$$

k represents the depth sample number associated with  $P_0$ ,  $f_s$  is the sampling frequency, and  $\chi$  is the interpolating weight between proximal depth samples.

To perform the LRI calculation, each receiving channel contribution is taken into account, but it is obvious that the receiving channels closer to the transmission channels have more important information, and therefore an arbitrary window function  $\psi$  will be applied:

$$\alpha_{n,m}[P_0] = \psi \times a_{n,m}[k] + (\psi - 1) \times a_{n,m}[k+1].$$

(2.24)

Given an arbitrary pixel  $P_0$ , its *m*-th LRI value is defined in the following way:

$$L_m[P_0] = \sum_{n=1}^{N} \psi_n \alpha_{n,m}[P_0], \qquad (2.25)$$

where  $L_m[P_0]$  is the value of pixel  $P_0$  of the *m*-th LRI.

# 2.5.4 HRI Compounding

Assuming that a full sweep of the transducer array corresponds to M firings, let's define the compounding of an HRI as:

$$H[P_0] = \sum_{m=1}^{M} L_m[P_0], \qquad (2.26)$$

where  $H[P_0]$  corresponds to the value of pixel  $P_0$ . When a new LRI is computed, the oldest LRI in the compounding frame is discarded, and the new one takes its place. Thus, it is possible to convert Eq. 2.26 into a more efficient [17]:

$$H_i[P_0] = H_{i-1}[P_0] + L_i[P_0] - L_{i-M}[P_0].$$

(2.27)

The process of compounding several LRIs to form an HRI corresponds to performing transmit beamforming, allowing for a more general focusing of the ROI, and improving the lateral resolution of the final image.

# 2.6 SA Beamforming vs. B-scan techniques

After conveying the reader with the working principles of both techniques, it is now time to discuss the advantages/disadvantages of the SA technique in comparison to the beamline-based technique:

| Advantages                         | Disadvantages                              |

|------------------------------------|--------------------------------------------|

| Ultra-High Frame-Rate Capability   | Higher Computational Complexity            |

| Transmit Beamforming Capability    | Current Hardware is not ready to implement |

| Improved Overall Image Quality     | SA beamforming techniques                  |

| Reduced Image Artefacts Appearance |                                            |

It would easily come to the mind of the reader that the preferred option should be the SA Beamforming technique, given its heightened image quality and frame-rate performance, but the disadvantages should also be taken seriously, since the computational workload required to implement the technique is significantly higher than that of typical B-scan techniques.

# 2.7 Conclusions

Concluding this chapter, it is expected that the readers now understand the principles behind beamline-based B-scan and SA Beamforming techniques, and can perform an assessment of the requirements and challenges faced by ultrasound systems engineers. It is the author's belief that SA Beamforming represents the future of medical ultrasound imaging systems, and that a parallel approach to the signal processing routine discussed in 2.5.2 and the use of programmable multi-core devices are the keys to address the disadvantages exposed in 2.6 and therefore, to achieve a working system, that can run on the standard personal computer or notebook, with improved image quality and real-time capability.

# 2. Ultrasound Theory and Imaging Algorithms

# 3

# Parallel Computing Frameworks and Manycore Devices

# Contents

| 3.1 | The Open Computing Language (OpenCL) Parallel Programming |  |  |  |  |  |  |

|-----|-----------------------------------------------------------|--|--|--|--|--|--|

|     | Model                                                     |  |  |  |  |  |  |

| 3.2 | The multicore CPU                                         |  |  |  |  |  |  |

| 3.3 | The manycore GPU         34                               |  |  |  |  |  |  |

| 3.4 | Conclusion                                                |  |  |  |  |  |  |

The rise and evolution of semiconductor technology over the last decades provided computing devices, such as Central Processing Units (CPUs) and Graphics Processing Units (GPUs) with growing computing capabilities. In recent years, physical limitations, especially tied to the core clock speeds and memory wall, implied that the scale of CPU cores could not increase, and thus the advent of multi-core CPUs became alternative. The initial role of the GPU was to perform multimedia tasks (video playback, graphics rendering) on the computer. The parallel nature of these devices, in conjunction with their multiple cores, and the development of programming constructs and interfaces lead to the rise of parallel programming, which allowed raising the throughput performance peak in other areas of general purpose computing. Since then, scientists in many fields have been employing the various parallel computing frameworks to implement compute-intensive algorithms.

In this chapter, the OpenCL framework is also discussed, as well as a brief discussion of current CPU and GPU architectures, emphasizing the latter, exposing through the section the main differences between Advanced Micro Devices (AMD) and NVIDIA GPUs.

# 3.1 The OpenCL Parallel Programming Model

OpenCL birthed from the industry's effort to design a general purpose parallel computing open standard. The OpenCL Application Programming Interface (API) currently supports both C and Fortran programming languages. This effort results in a wide range of compatible multi-core devices available in the market. Although CPUs are able to run OpenCL kernels, the framework is optimized for GPUs.

A single kernel code, running efficiently on several devices is one of the main goals of OpenCL, therefore, there is a low-level of hardware abstraction.

In this section, for illustrative purposes the figures will be related to a sample program whose objective is to perform the parallel summation of two single floating-point matrices (A and B) and store the result in matrix C. The computing workload associated with this algorithm is not very high, but it works perfectly as a demonstrative program.

# **3.1.1 Platform Model**

In an OpenCL program, there must be distinction between the host code and the device code. The first will query the available parallel platforms and respective devices, allocate device memory, and overall perform flow control. The latter is the parallel section of the code, the kernel itself, and runs on the queried devices.

The mere presence of an OpenCL supported device in the machine is not sufficient to guarantee that the device is able to run OpenCL kernels. In order to achieve that, the

vendor's OpenCL Software Development Kit (SDK) must be installed in the machine. Fig. 3.1 illustrates the process of querying the machine for OpenCL supported devices:

```

//OpenCL Device Query Code

char pbuff[100]; //Char Buffer to hold the name of the devices

cl_int err; //Error Controlling Variable

cl_uint numPlatforms;

cl_uint numDevices;

//First call to get the number of available platforms

err = clGetPlatformIDs(0,NULL,&numPlatforms);

//Allocate space for all the available platforms

cl_platform_id* platforms = (cl_platform_id *)malloc(numPlatforms*sizeof(cl_platform_id));

//Query the platforms

err = clGetPlatformIDs(numPlatforms,platforms,NULL);

//Choose the first (Assuming error-free execution, for space constraint reasons)

cl_platform_id cPlatform = platforms[0];

//For the chosen platform, query the number of available devices

err = clGetDeviceIDs(cPlatform,CL_DEVICE_TYPE_ALL,0,NULL,&numDevices);

//Allocate space for all the available devices

cl_device_id *devices = (cl_device_id *)malloc(numDevices*sizeof(cl_device_id));

//Query the devices

err = clGetDeviceIDs(cPlatform,CL_DEVICE_TYPE_ALL,numDevices, devices, NULL);

for(int i=0; i<numDevices; i++)</pre>

//Get the info of each device, and print it iteratively

err = clGetDeviceInfo(devices[i], CL_DEVICE_NAME, sizeof(pbuff), pbuff, NULL);

printf("\%s\setminus n",pbuff);

}

cl_device cDevice = devices[0];

cl_context cContext = clCreateContext(0, 1, &cDevice, NULL, NULL, &err);

/*...*/

//Free the allocated memory

free(platforms);

free(devices);

```

Figure 3.1: OpenCL Device Query.

# 3.1.2 Runtime Model

The fact that OpenCL can be run in different types of devices, adds a new layer of complexity to the programming process. While NVIDIA only provides OpenCL support for their GPUs, Intel provides support for proprietary devices (CPUs and GPUs), AMD provides support for all devices except NVIDIA and Intel integrated GPUs. To generate a kernel executable, each device may require different binaries. For that reason, and because

the device query and selection is only performed at runtime, the building, compiling, linkage and executable generation of the *kernel* can only occur during runtime. Generally OpenCL *kernels* are either stored in a separate file (the common extension is **.cl**) or directly stored in a string in the main C/C++ file. [19] [20]

#### 3.1.2.A Command-queues

All OpenCL objects, either being *devices*, *platforms*, *queues*, or *programs* share the fact that all operations performed on them must be enqueued in a *command-queue*. This *command-queue* is bound to a specific *device*, and by default the operations are performed in-order, and synchronization is implicitly guaranteed. It is possible to alter this behaviour, allowing for out-of-order queue execution. However, the synchronization between commands must be ensured by using *events*. This is required, for example, when implementing overlapping the memory transfers and *kernel* executions (see Sec. 3.1.2.D). Fig. 3.2 illustrates the creation of a *command-queue* with default options (the third argument is empty).

/\* ... \*/

cl\_command\_queue cQueue = clCreateCommandQueue(cContext, cDevice, NULL, &err);

/\* ... \*/

Figure 3.2: OpenCL Queue Creation.

#### 3.1.2.B Memory Model and Allocation

Given the interoperability between different devices, even when running the OpenCL kernels on CPUs, there must be separation between host memory and device memory. To run an OpenCL *kernel*, the programmer must ensure that the required input and output *device buffers* are allocated, and properly data-filled before the *kernel* execution can occur. The fact that OpenCL is supposed to run on a multitude of *devices*, introduces a new level of complexity, since different *devices* have different memory regions (more on this on Sec. 3.3.2) and sizes, and thus, the programmer must also imbue the program with the necessary conditions to attain resource adaptability.

There are two ways to perform memory transfers: either synchronously by queueing the transfer, or asynchronously by mapping the buffer with pointers in the *device/host*. Fig. 3.3 shows the creation of the synchronous and asynchronous *buffers*.

```

/* ... */

float array[5] = {1.0,2.1,3.2,4.3,5.4} //input data to be transferred to the buffers

cl_mem cBuffer_1, cBuffer_2;

//cBuffer_1 will be created with queueable data transfers

cBuffer_1 = clCreateBuffer(cContext,CL_MEM_READ_ONLY,sizeof(cl_float)*5,NULL,&err);

err = clEnqueueWriteBuffer(cQueue,cBuffer_1,CL_FALSE,0,sizeof(cl_float)*5,array,NULL, ...

... NULL,NULL);

//cBuffer_2 will be created for mapping in the device

cBuffer_2 = clCreateBuffer(cContext,CL_MEM_READ_ONLY | CL_USE_HOST_PTR, ...

... sizeof(cl_float)*5, NULL,&err);

clEnqueueMapBuffer(cQueue,cBuffer_2,CL_FALSE,CL_MAP_READ,0,sizeof(float)*5,NULL,NULL, ...

... NULL,&err);

/* ... */

```

Figure 3.3: OpenCL Buffer Creation and Mapping/Enqueuing.

After execution, the output buffer is read from the device.

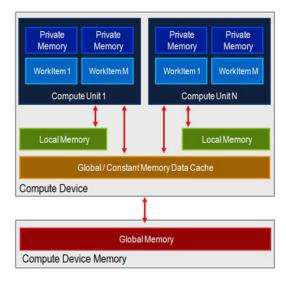

OpenCL defines several address spaces, where the buffers can be allocated or mapped, according to the desired usage and requirements. These are *\_\_global*, *\_\_local*, *\_\_private* and *\_\_constant*. The *\_\_global* is accessible to all work-items in the context, and it is also the largest (and slowest) address space. *\_\_local* is specific to each work-group, and thus only the work-items of a given work-group can read/write from/to this memory region. *\_\_constant* is a read-only memory region, accessible by every work-item, faster than global memory, and ideal for variables initialized in the host, that won't suffer changes throughout the kernel execution. Finally, *\_\_private* is specific to each work-item. It is excellent to store temporary data, as it is the fastest type of memory.

Figure 3.4: OpenCL Address Space. [2]

#### 3.1.2.C Kernel Work Size and Execution

A parallel implementation of a serial algorithm consists of the division of the work into small work units. For the example summation program considered, each work unit corresponds to an element of the buffer. In OpenCL, each of these small units is called *work-item*. A *work-group* is a group of *work-items*. Depending on the nature of the algorithm and the *device* capabilities, the *work-group* might have 1, 2 or even 3 dimensions. The optimal solution regarding the number of *work-items* per *work-group* must be determined by experiment (although OpenCL profilers use a few metrics to determine the point of "optimal" performance, the proposed solutions often return non-optimal results). The size of a *work-group* is called the *local work size*. The total number of *work-items* required by the algorithm determines the *global work size*, whose value must always be a multiple of the *local work size* (if more than one dimension is used, all the dimensions must be multiples).

After the input *buffers* are filled, and the work dimensions are set, the *kernel* is enqueued and executed.

#### 3.1.2.D Optimization Strategies

The main goal of parallel computing consists of using the resources in an efficient way. Therefore, when designing an OpenCL *kernel*, there are a few rules that can significantly improve the program's performance:

- Thread Divergence: A wavefront is the execution of *N* OpenCL *work-items* in parallel, on AMD GPUs. On NVIDIA GPUs, while the exact concept is not replicated, because of the different nature of the architecture, the basic principle applies, but it is called a warp. When the *kernel* is being executed, consecutive *work-items* are grouped for execution. When a divergent condition is present (such as an *if* statement), the wavefront/warp will have to check both paths of execution, resulting in an additional cycle. In the limit all threads/work-items can follow a different path and execution serializes. Therefore, whenever possible, divergent branches should be eliminated.

- Coalesced Memory Accesses: Most current computers are equipped with dual channel Random Access Memory (RAM), that ensure that the width of the memory bus to the CPU is 128-bit. Similarly, the Peripheral Component Interconnect Express (PCIe) 3.0 currently used by most mid-level GPUs also feature a bus width of 128-bit. When the *kernel* is running, and the work-items in a warp/wavefront perform a memory load, the device is smart enough to detect if the addresses being read by consecutive work-items are consecutive or separated by a constant stride multiple of 16 or 32. When such event occurs, such as in the matrix summation sample, the program coalesces multiple memory accesses into a single access, thus largely reducing the number of memory operations/transactions.

- Use of registers: The number of private registers (See 3.3.2) depends on the device, but they can be used to store temporary data, or to reduce the number of accesses to the global memory.

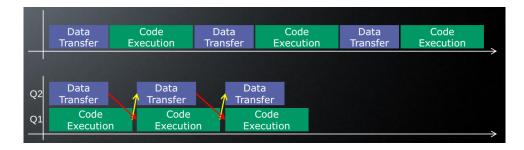

- Asynchronous Memory Transfers: Frequently, the main performance bottleneck in OpenCL applications are the memory transfers. By using two *queues* bound to the same device, additional buffers and events to guarantee synchronization between queues, it is possible to overlap memory transfers with kernel execution, increasing the overall throughput of the program.

Figure 3.5: OpenCL Kernel Execution/Memory Operations Overlapping. [3]

With this exposition, the reader is expected to better understand the advantages and potential behind the use of parallel programming, particularly with the OpenCL framework, allowing for one code to run on multiple devices, crossing different architectures, different vendors and even different types of devices.

# 3.2 The multicore CPU

In 1965, Gordon Moore predicted that, until 1975, every two years the number of transistors per integrated circuit would double [21]. Little did he know back then, that his predictions were not only spot-on for that span of time, but it also set objectives for the computing hardware and semiconductor industry, and these goals are still being sought as of today.

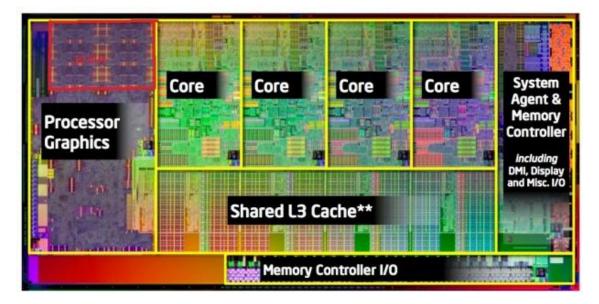

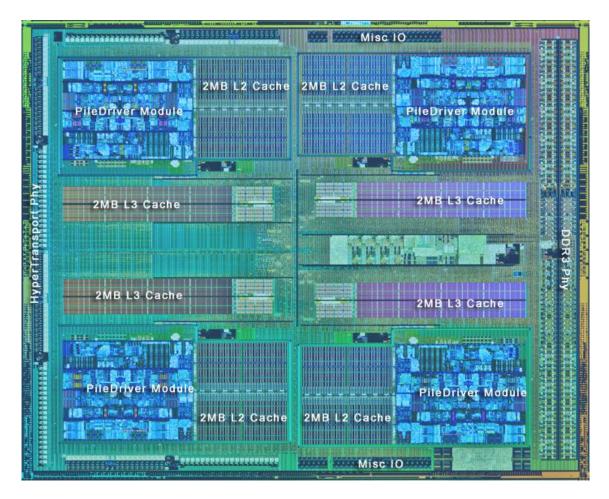

CPUs are just "victim" of this growth, and if in 1980, the Intel 80186 featured 29000 transistors, in 1993 the original Pentium processor already had more than 3 million transistors. To further increase the performance of CPUs to meet the ever-increasing industry needs, the clock speed of the transistors also increased. But physical limitations regarding heat dissipation, and the fact that the growth in clock speed had stalled, led to the pursuit of new ways to increase the performance. Thus, the rise of the multicore CPU era. Multicore CPUs provide parallel resources, and the power constraints are not so constrictive, making these the viable solution, to keep supplying the users with performance increments. Fig. 3.6 and Fig. 3.7 show the die of the Haswell and Piledriver architectures from Intel and AMD, respectively.

Let us now discuss the general architecture of multicore CPUs, starting with the Control Unit:

Figure 3.6: Intel Haswell architecture die. [4]

# 3.2.1 Control Unit

The control unit of a core, as its name says, corresponds to the group of circuits in the chip that is responsible for controlling the fetching of instructions from memory, decoding the instruction and memory addresses of the operands for the operation, redirects the data to the arithmetic and logic units, so that the desired operation may be performed. It also controls the flow of data between all the devices in the computer. The instruction set of the CPU is also implemented in the control unit.

# 3.2.2 Arithmetic and Logic Unit (ALU)

The ALU is the group of logic circuitry present in each core that is responsible for performing every arithmetic operations like additions, subtractions, multiplications, bit shifting, logic operations such as AND, OR, NOT and boolean comparisons. Operations performed by ALUs are the basis for more complex instructions. Current CPUs' ALUs provide support for floating-point operations, which leads to the understandable conclu-

Figure 3.7: AMD Piledriver architecture die. [5]

sion that, nowadays, ALUs are components of very complex design, and this design is different between different CPUs models.

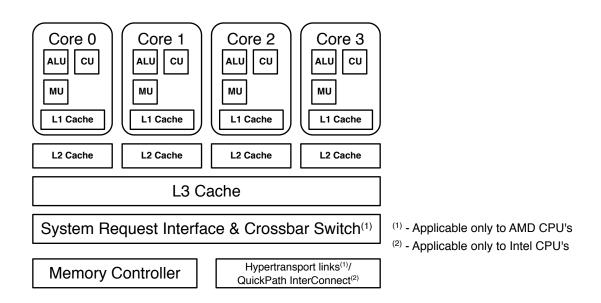

# 3.2.3 Memory Interface and Caches

The system memory is basically comprised of three types of memory: Dynamic Random Access Memory (DRAM), Read Only Memory (ROM) and cache memory. While the caches are a feature of the CPU, DRAM and ROM are not located in the chip itself, as they are placed on the motherboard. Here, an appointment must be made regarding a major difference between the two main CPU vendors, Intel and AMD. Until recent years, Intel CPUs communicated with the DRAM and ROM through the motherboard memory controller, the Front-Side Bus (FSB). But recently, Intel improved its system, implementing the QuickPath InterConnection technology. This technology, as all AMD CPUs, features native memory controllers. For the sake of retro compatibility, since there are still many computers using FSB, its principles are briefly discussed below.

Figure 3.8: Current generation quadcore CPU basic diagram. Intel and AMD CPUs differences are highlighted.

#### 3.2.3.A DRAM and ROM