João Pedro Aleixo Duarte

# AQUISIÇÃO DE IMAGENS ATRAVÉS DE FPGA

(IMAGE ACQUISITION WITH FPGA)

Dissertação de Mestrado Mestrado Integrado em Engenharia Electrotécnica e de Computadores

Setembro de 2015

#### Universidade de Coimbra Faculdade de Ciências e Tecnologia Departamento de Engenharia Eletrotécnica e de Computadores

Mestrado Integrado em Engenharia Eletrotécnica e de Computadores

# Aquisição de Imagens através de FPGA

(Image Acquisition with FPGA)

João Pedro Aleixo Duarte

Trabalho desenvolvido sob supervisão de: Tony Richard de Oliveira de Almeida (DEEC - FCTUC) Jorge Manuel Simões de Almeida (CRITICAL Software, SA)

Júri:

António Paulo Mendes Breda Dias Coimbra Gabriel Falcão Paiva Fernandes Tony Richard de Oliveira de Almeida

Com o apoio de iTGROW Trabalho desenvolvido nas instalações da CRITICAL Software, SA no Parque Industrial de Taveiro

### **Agradecimentos**

Queria começar por agradecer àqueles que contribuíram de forma mais directa para este trabalho. Ao meu orientador, o Professor Tony Richard, pela disponibilidade e simpatia que sempre demonstrou ao longo de todo o processo. A todos os colaboradores da CRITICAL Software, em especial ao Álvaro Lopes, Humberto Rodrigues, Jorge Almeida, José Rui Simões e Paulo Fernandes pela ajuda, aconselhamento e apoio que foram dando durante estes últimos meses. Aos outros, onde incluo os "iTGrow'ers", obrigado pela estima e carinho que tenho recebido.

Agradeço também àqueles que me apoiam e amparam: à minha família e amigos por estarem sempre ao meu lado.

Aos que me acompanharam neste percurso académico: desde colegas, professores e à restante comunidade do DEEC, por terem, todos eles, contribuído de alguma forma para o meu crescimento.

A todos, o meu sincero obrigado.

**Abstract**

In this work, it was intended to proceed with the capture of images that are sent to the display

of a completely digital dashboard for automotive applications, by the graphic processor, for future

comparison. The project also wants to confirm that FPGAs (Field-Programmable Gate Arrays) can

be a viable alternative to frame grabbers, ASICs (Application Specific Integrated Circuits) or

simply other processors and microcontrollers in this type of application, for being able to acquire

images in real-time at the same frame rates that they are being sent, i.e. without down sampling.

The FPGAs also allow to reduce costs and development times due to its flexibility and efficiency.

It was used an FPGA ZedBoard (Zyng Evaluation and Development Board) for developing

this project and it was also necessary to design and produce a printed circuit board (PCB) which

is an essential element in the connection between the FPGA, the instrument cluster board and its

display.

At the time, it was designed and ready to implement in FPGA a hardware and software

platform, capable of capturing images. The system was successfully tested in simulation

environment and it is ready for tests in real situations that will confirm its correct operation.

Therefore, there is a baseline for concrete results, in the near future.

The next step would be an image comparison (image difference or pattern comparison)

between the captured images and reference images, to confirm that the information presented by

the instrument cluster's display is in accordance with the "stimuli" sent (mostly CAN messages),

simulating the various vehicle equipments.

**Keywords:** display, FPGA, instrument cluster, PCB, real-time image acquisition, ZedBoard.

V

### Resumo

Neste trabalho pretendia-se proceder à captura das imagens a serem enviadas para o ecrã de um painel de instrumentos de aplicação na indústria automóvel, completamente digital, pelo processador gráfico, para futura comparação. Quer também confirmar que as FPGAs (<u>Field-Programmable Gate Arrays</u>) podem ser uma alternativa viável, a *frame grabbers*, ASICs (<u>Application Specific Integrated Circuit</u>) ou outros processadores e microcontroladores, neste tipo de aplicação ao serem capazes de adquirir as imagens em tempo real, ao mesmo ritmo a que as *frames* estão a ser enviados, *i.e.* sem ser necessário qualquer tipo de subamostragem. As FPGAs permitem também reduzir os custos e períodos de desenvolvimento devido à sua flexibilidade e eficiência.

Usou-se uma FPGA ZedBoard (Zynq <u>Evaluation and Development Board</u>) para o desenvolvimento deste projecto, tendo sido também necessário projectar e produzir uma placa de circuito impresso (PCB) que é um elemento essencial na ligação entre a FPGA, a placa do painel de instrumentos e o ecrã do mesmo.

À data, ficou projectada e pronta a implementar na FPGA uma plataforma de *hardware* e *software*, capaz de capturar imagens. O sistema foi testado com sucesso em ambientes simulados e está pronto para testes em situações reais que confirmarão a sua correcta operação. Está criada a base para chegar a resultados concretos, num futuro próximo.

O próximo passo será uma comparação das imagens (ou pela diferença das imagens ou por comparação de padrões) entre as imagens capturadas e imagens de referência, para confirmar que a informação apresentada pelo ecrã está de acordo com os "estímulos" enviados (sobretudo mensagens CAN), simulando os vários equipamentos do veículo.

**Palavras-chave:** ecrã, FPGA, painel de instrumentos, PCB, aquisição de imagens em tempo-real, ZedBoard.

# Índice

| Agradecimentos                                                  | iii  |

|-----------------------------------------------------------------|------|

| Abstract                                                        | v    |

| Resumo                                                          | vii  |

| Índice                                                          | ix   |

| Lista de Figuras                                                | xiii |

| Lista de Figuras (Anexos)                                       | xiv  |

| Lista de Tabelas                                                | xiv  |

| Acrónimos e Unidades                                            | xvii |

| 1 Introdução                                                    | 1    |

| 1.1 Motivação                                                   | 1    |

| 1.2 Objetivos                                                   | 2    |

| 1.3 Estrutura da dissertação                                    | 2    |

| 2 Estado da arte                                                | 5    |

| 2.1 Principais contribuições                                    | 6    |

| 3 Painel de instrumentos                                        | 9    |

| 4 Ligação com o ecrã                                            | 17   |

| 5 Escolha da FPGA                                               | 23   |

| 6 Arquitectura                                                  | 27   |

| 6.1 Arquitectura física                                         | 27   |

| 6.2 Arquitectura do caminho de dados (datapath)                 | 30   |

| 7 Implementação                                                 | 35   |

| 7.1 Vivado Design Suite                                         | 35   |

| 7.2 Construção do <i>datapath</i>                               | 36   |

| 7.2.1 Desenvolvimento de software                               | 41   |

| 7.2.2 Notas sobre Interfaces AXI                                | 42   |

| 7.2.3 Módulos criados                                           | 43   |

| 7.3 Testes ao datapath                                          | 51   |

| 7.3.1 Test benches                                              | 51   |

| 7.3.2 Integração dos módulos de debug na plataforma de hardware | 55   |

| 7.3.3 Mark Debug                                                | 55   |

| 7.3.4 Testes ao datapath completo                               | 56   |

| 8 Montagem do sistema                                           | 63   |

| 8.1 Projecto da PCB de interface                                | 63   |

| 8.2 Ligação     | dos equipamentos e testes ao sistema                                   | 66      |

|-----------------|------------------------------------------------------------------------|---------|

| 9 Trabalho comp | lementar                                                               | 69      |

| 9.1 Módulos     | adicionais implementados                                               | 69      |

| 9.2 Possíveis   | s melhoramentos                                                        | 70      |

| 9.2.1 Env       | io da informação para outra máquina                                    | 70      |

| 9.2.2 Mul       | tiprocessamento assimétrico                                            | 72      |

| 9.2.3 Inter     | rfaces Pmod                                                            | 72      |

| 9.2.4 Saíd      | las de vídeo da ZedBoard                                               | 73      |

| 9.2.5 Proj      | ecto de PCBs de interface alternativas                                 | 74      |

| 10 Conclusões   |                                                                        | 77      |

| Referências     |                                                                        | 81      |

| Anexos          |                                                                        | 89      |

| Anexo A - E     | xemplos de código desenvolvido                                         | 91      |

| A - 1) pa       | ttern_generator.vhd                                                    | 91      |

| A - 2) fra      | ame_ram.vhd (versão inicial)                                           | 95      |

| A - 3) fra      | ame_ram.vhd (versão 2, com integração de FIFO e interface com RAM)     | 98      |

| A - 4) pa       | ttern_generator_tb.vhd                                                 | 102     |

| A - 5) Fr       | ameRAMwAXI_v1_0.vhd                                                    | 104     |

| A - 6) ma       | ain.c (aplicação que configura o módulo VDMA e o controlador           | HDMI    |

| via             | a I <sup>2</sup> C)                                                    | 110     |

| Anexo B - In    | nagens de alguns projectos criados                                     | 121     |

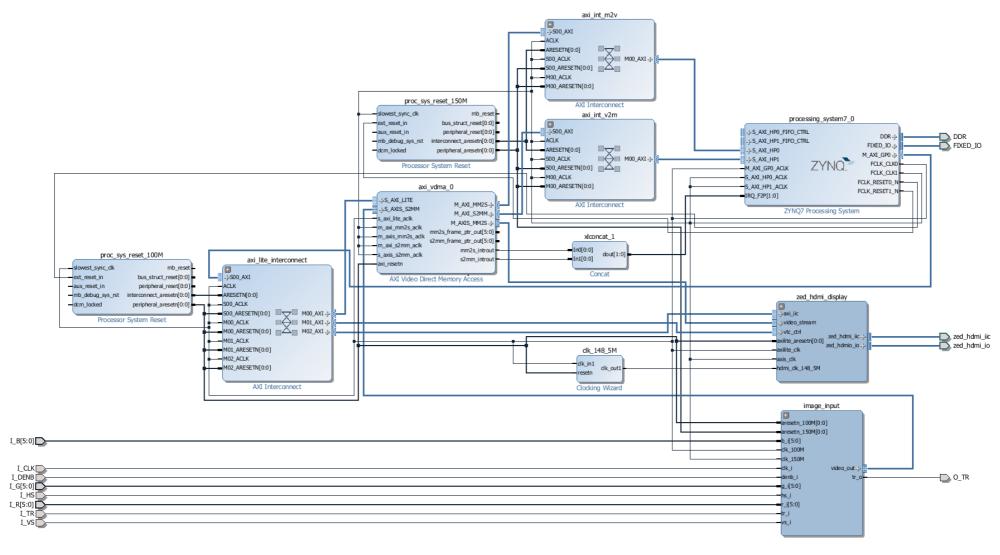

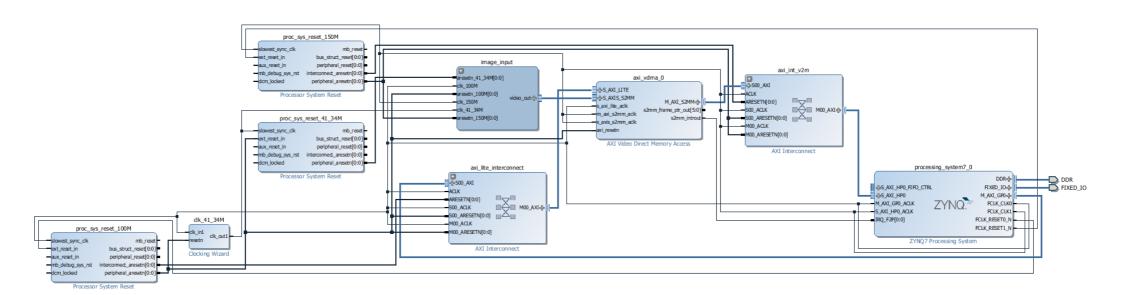

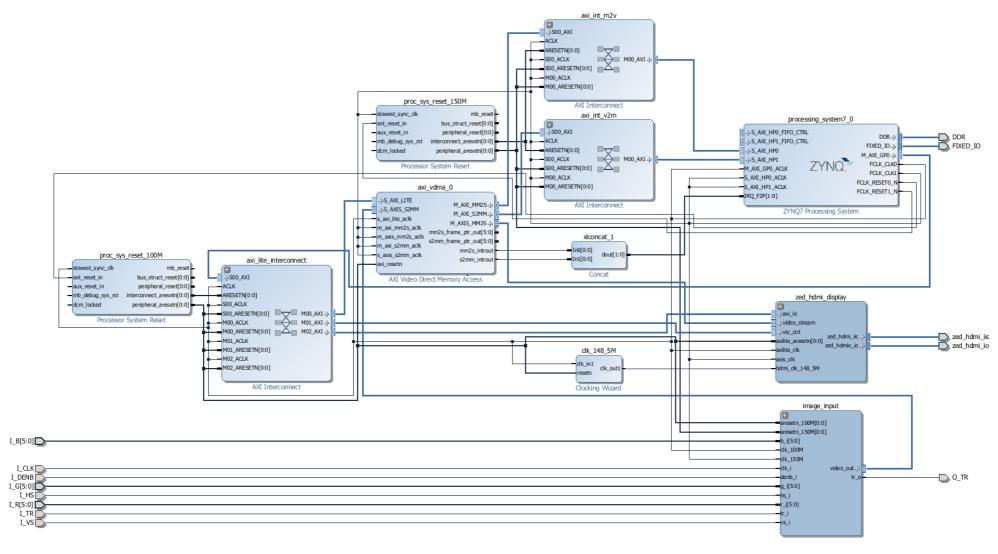

| B - 1) Di       | agrama de blocos - datapath completo (versão minimal)                  | 121     |

| B - 2) Po       | ormenor do diagrama de blocos - datapath completo (versão minimal)     | 122     |

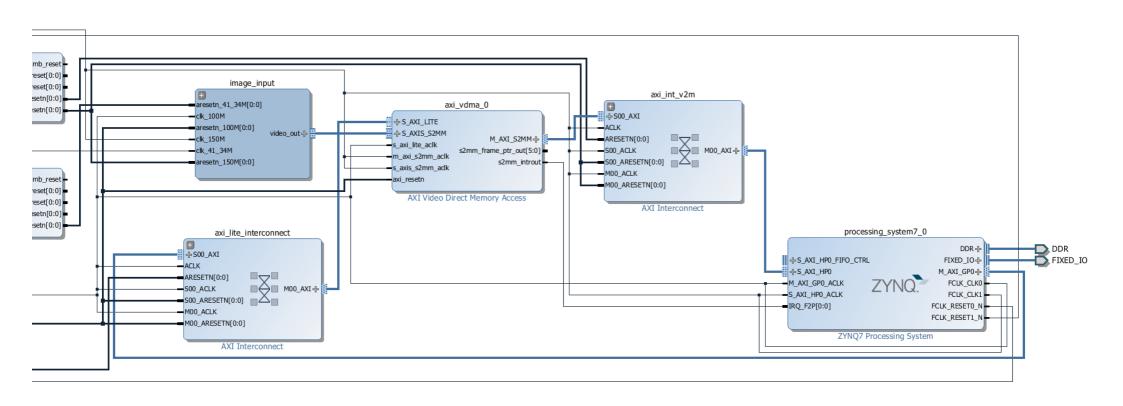

| B - 3) Di       | agrama de blocos - bloco "image_input"                                 | 123     |

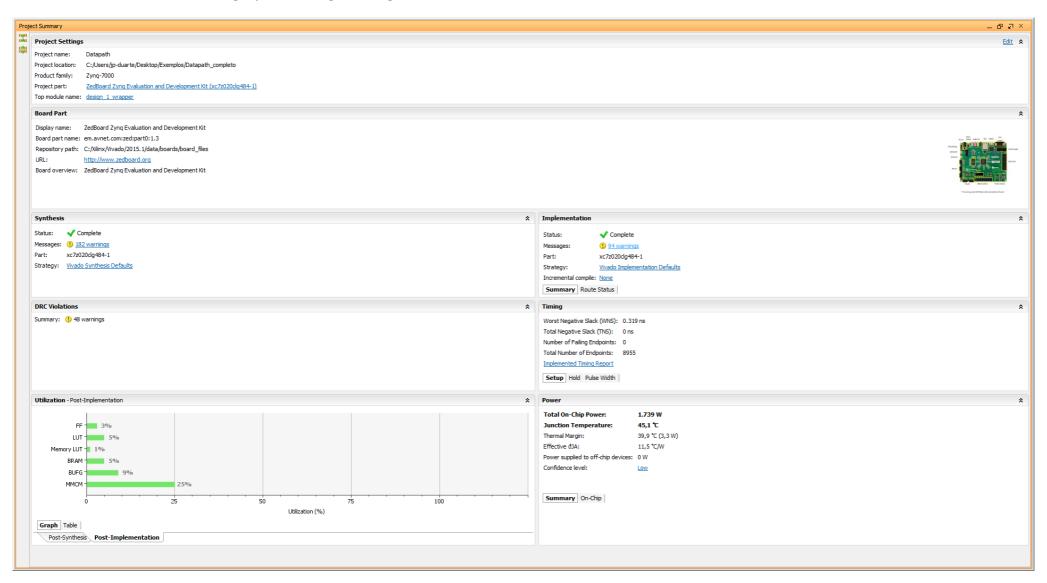

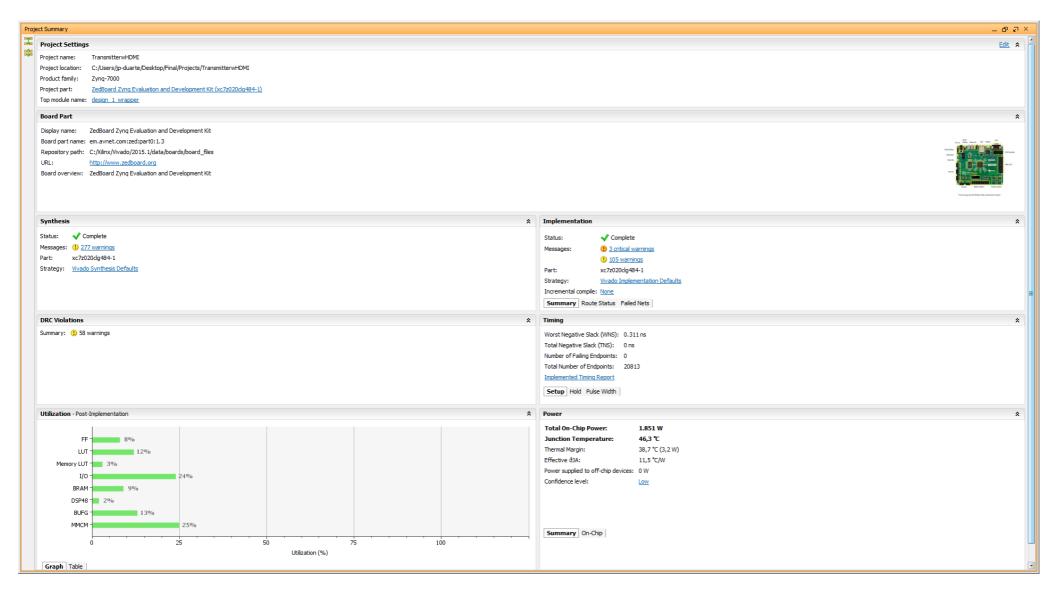

| B - 4) Re       | elatório sumário do projecto - datapath completo (versão minimal)      | 124     |

| B - 5) Di       | agrama de blocos - datapath completo (versão com entrada de vídeo      | externa |

| e s             | saída HDMI)                                                            | 125     |

| B - 6) Re       | elatório sumário do projecto - datapath completo (versão com entrada d | e vídeo |

| ex              | terna e saída HDMI)                                                    | 126     |

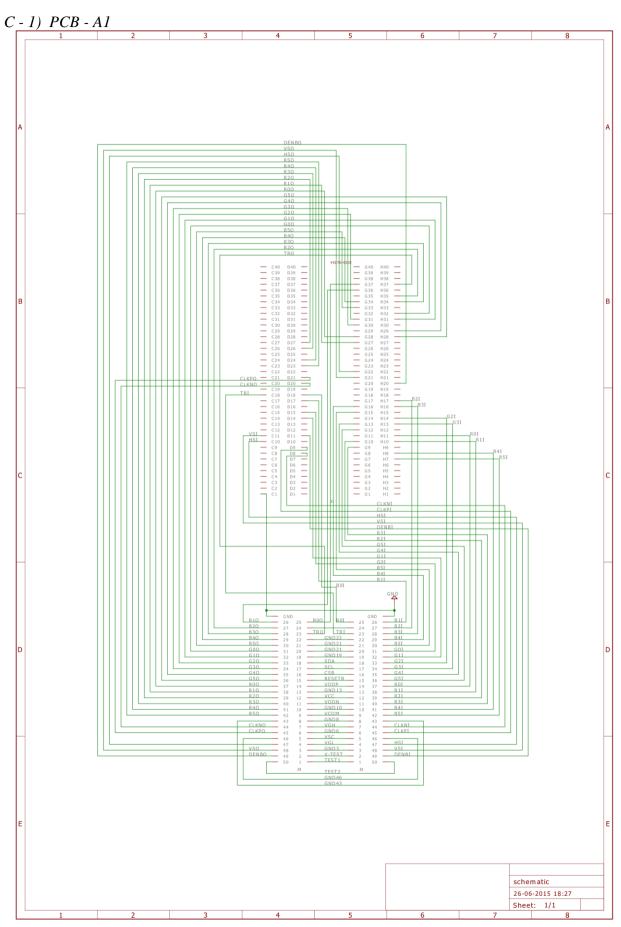

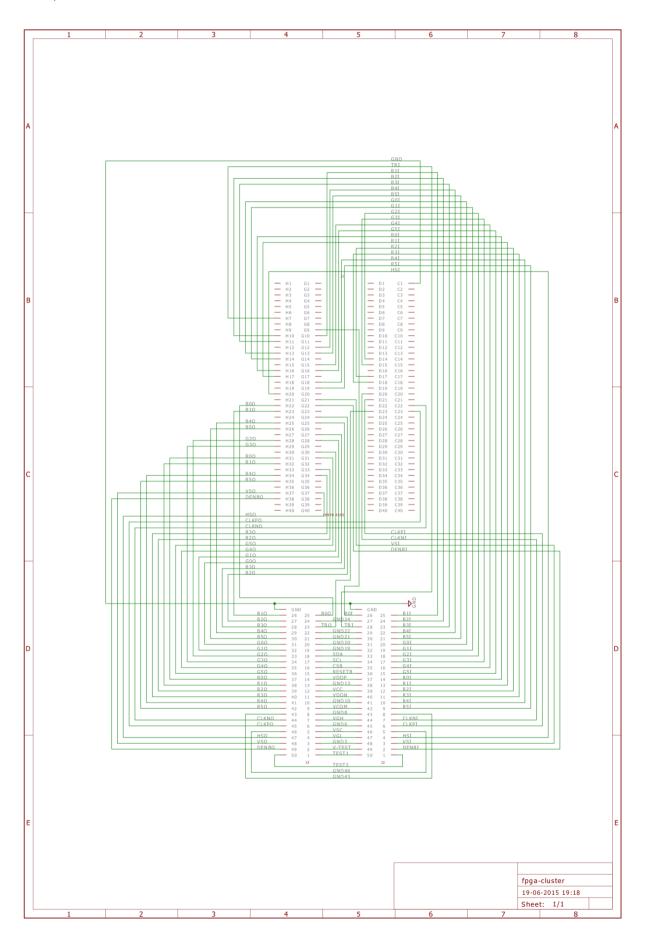

| Anexo C - D     | esenhos esquemáticos das PCB (alternativas)                            | 129     |

| C - 1) PC       | B - A1                                                                 | 129     |

| C - 2) PC       | B - A2                                                                 | 130     |

# Lista de Figuras

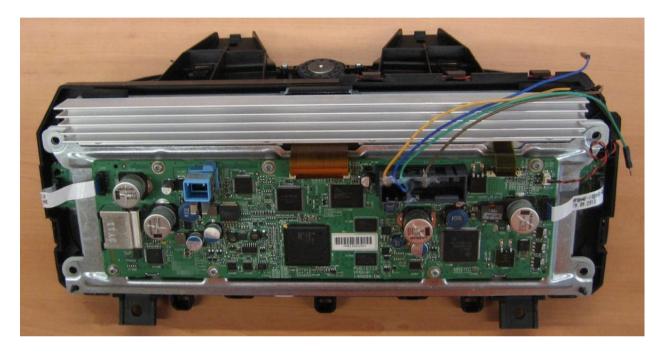

| Figura 1 - Fotografia do painel de instrumentos (frente)                                  | 9      |

|-------------------------------------------------------------------------------------------|--------|

| Figura 2 - Fotografia do painel de instrumentos (trás)                                    | 10     |

| Figura 3 - Diagrama com a definição das fronteiras e interfaces do painel de instrumentos | 11     |

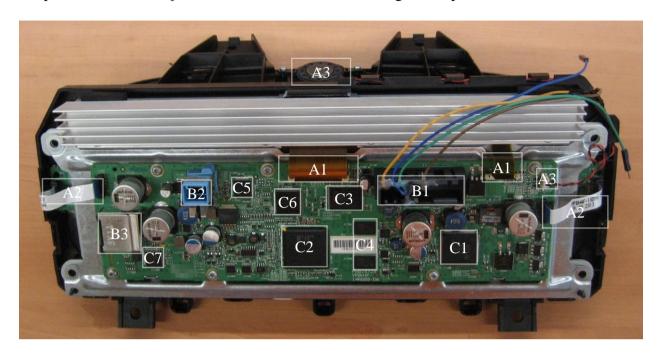

| Figura 4 - Fotografia com a placa do painel de instrumentos                               | 12     |

| Figura 5 - Fotografia com a placa do painel de instrumentos (com anotações)               | 13     |

| Figura 6 - Esquema mais detalhado das interfaces entre componentes do painel de instrur   | nentos |

| e/ou restantes elementos do veículo                                                       | 13     |

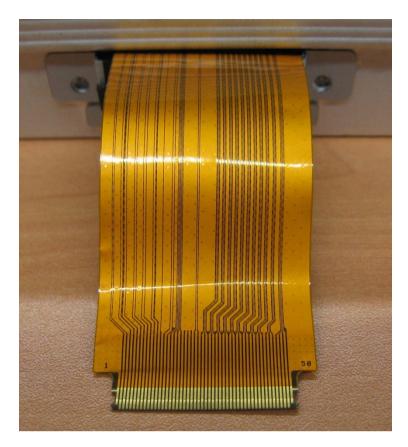

| Figura 7 - Foto do FPC principal do ecrã                                                  | 18     |

| Figura 8 - Foto do FPC principal do ecrã (com anotações)                                  | 19     |

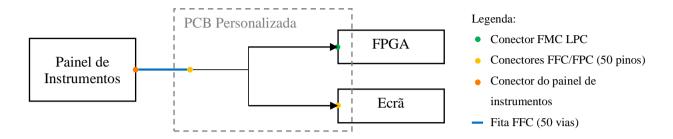

| Figura 9 - Ilustração da primeira hipótese de arquitectura física                         | 29     |

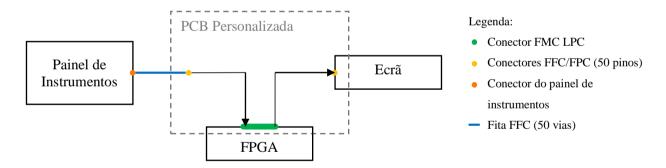

| Figura 10 - Ilustração da segunda alternativa de arquitectura física                      | 29     |

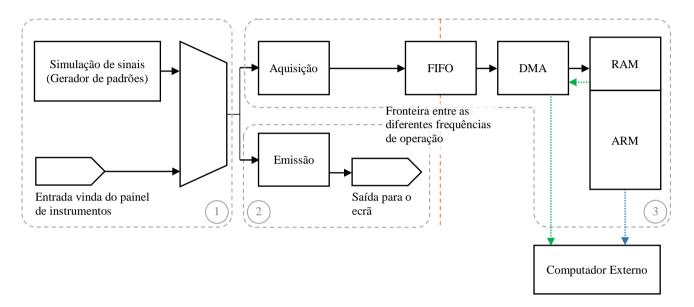

| Figura 11 - Diagrama de blocos da arquitectura do caminho de dados                        | 30     |

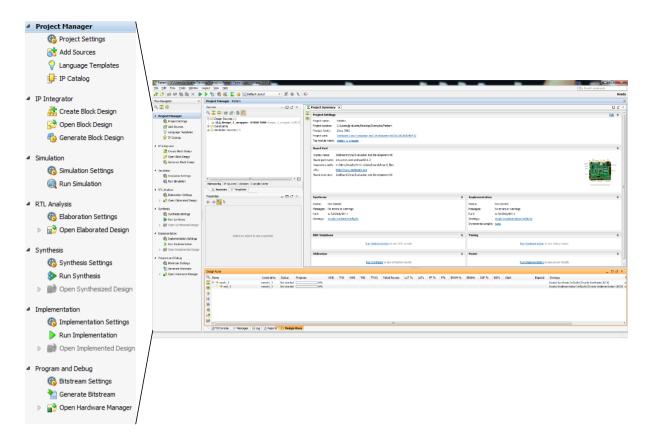

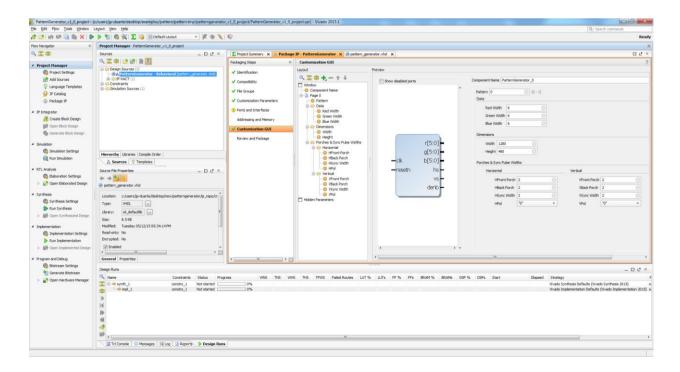

| Figura 12 - Interface principal da suite Vivado com destaque para o "Flow Navigator"      | 36     |

| Figura 13 - Diagrama de blocos (esquemático) da implementação básica                      | 37     |

| Figura 14 - (a) Diagrama de blocos da implementação básica;                               |        |

| (b) Pormenor do diagrama                                                                  | 38     |

| Figura 15 - Composição do bloco "image_input"                                             | 39     |

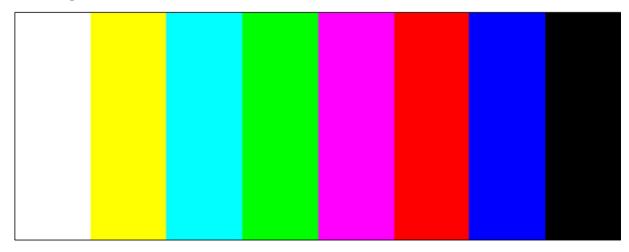

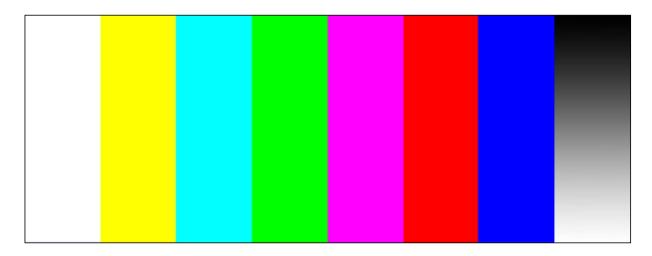

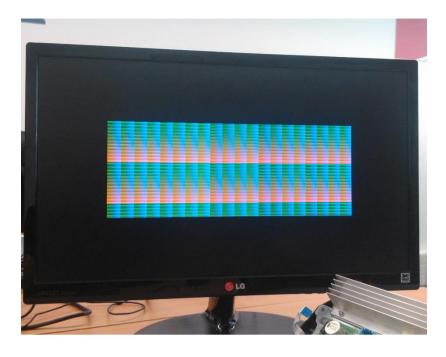

| Figura 16 - Representação dos padrões de barras de cor (versão original) (formato 8:3)    | 47     |

| Figura 17 - Representação dos padrões de barras de cor (versão final) (formato 8:3)       | 48     |

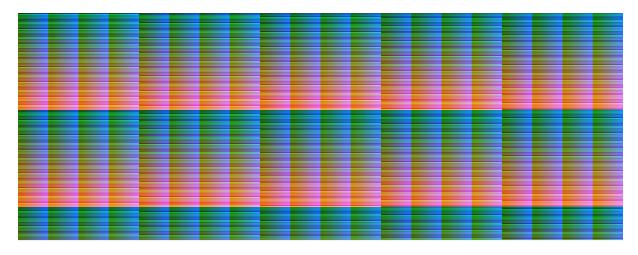

| Figura 18 - Representação do segundo padrão (18 bits menos significativos da posição (RGI | 3666)) |

| (formato 8:3)                                                                             | 50     |

| Figura 19 - Aspecto da aplicação aquando a criação de IP cores                            | 50     |

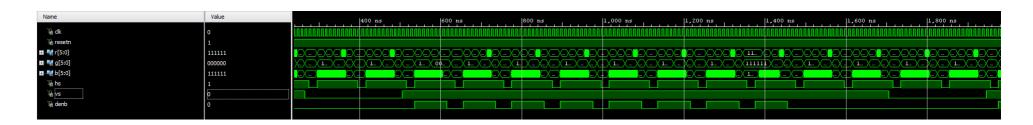

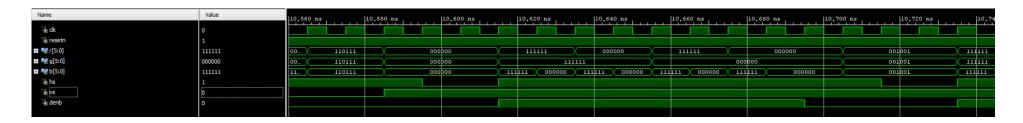

| Figura 20 - Diagrama temporal dos sinais do módulo "gerador de padrões" (1 frame, 8x8) .  | 54     |

| Figura 21 - Diagrama temporal dos sinais do módulo "gerador de padrões"                   |        |

| (1 linha, 8 colunas)                                                                      | 54     |

| Figura 22 - Linha assinalada com a opção "Mark Debug"                                     | 55     |

| Figura 23 - Diagrama de blocos esquemático do datapath (com saída HDMI)                   | 56     |

| Figura 24 - Diagrama de blocos esquemático do datapath (monitores de memória)             | 57     |

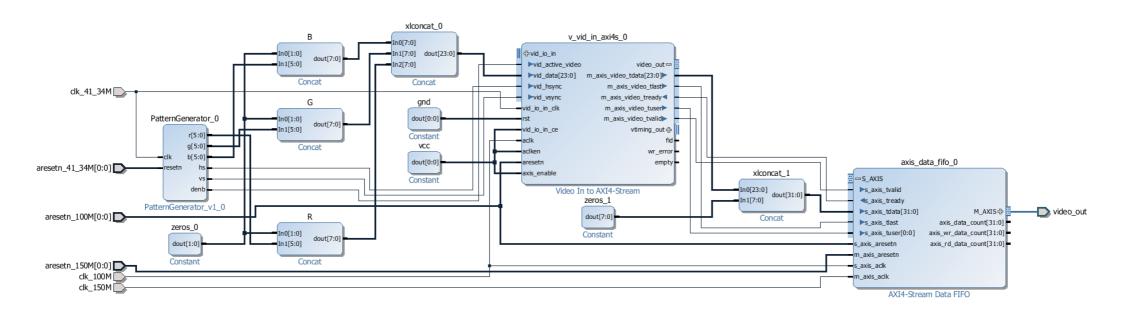

| Figura 25 - Diagrama de blocos do datapath (versão com entrada externa e saída HDMI)      | 60     |

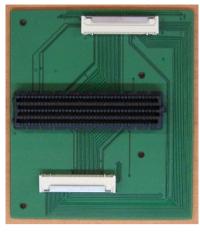

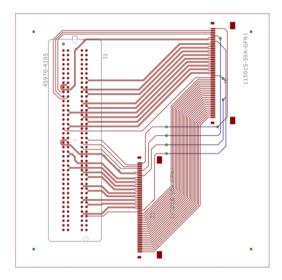

| Figura 28 - Desenho da PCB criada (board)                                                 | 65     |

| Figura 28 - Fotografia da PCB criada (face inferior)                                      | 65     |

| Figura 28 - Fotografia da PCB criada (face superior)                                    | 65          |

|-----------------------------------------------------------------------------------------|-------------|

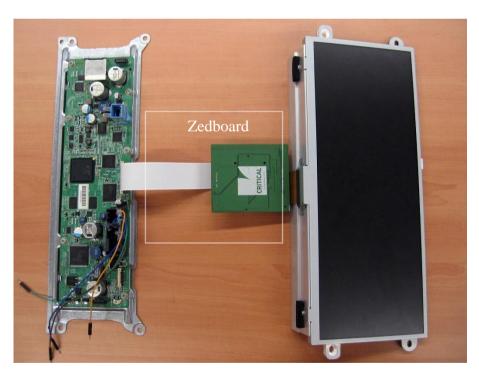

| Figura 29 - Ilustração da montagem efectuada                                            | 66          |

| Figura 30 - Fita FFC utilizada na ligação                                               | 67          |

| Figura 31 - Fotografia do ecrã ligado à saída de vídeo externa (HDMI)                   |             |

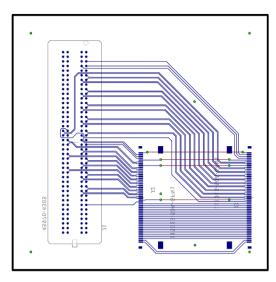

| Figura 32 - Desenho da nova PCB (A1)                                                    |             |

| Figura 33 - Desenho da nova PCB (A2)                                                    | 75          |

|                                                                                         |             |

|                                                                                         |             |

| Lista de Figuras (Anexos)                                                               |             |

|                                                                                         |             |

| 1 - B - 1) Diagrama de blocos - datapath completo (versão minimal)                      | 121         |

| 2 - B - 2) Promenor do diagrama de blocos - datapath completo (versão minimal)          | 122         |

| 3 - B - 3) Diagrama de blocos - bloco "image_input"                                     | 123         |

| 4 - B - 4) Relatório sumário do projecto - datapath completo (versão minimal)           | 124         |

| 5 - B - 5) Diagrama de blocos - datapath completo (versão com entrada de vídeo          | externa e   |

| saída HDMI)                                                                             | 125         |

| 6 - B - 6) Relatório sumário do projecto - datapath completo (versão com entrada de vío | deo externa |

| e saída HDMI)                                                                           | 126         |

| 7 - C - 1) Desenho esquemático da PCB alternativa 1 (PCB A1)                            | 129         |

| 8 - C - 2) Desenho esquemático da PCB alternativa 2 (PCB A2)                            | 130         |

|                                                                                         |             |

|                                                                                         |             |

|                                                                                         |             |

| Lista de Tabelas                                                                        |             |

|                                                                                         |             |

|                                                                                         |             |

| Tabela 1 - Lista de algumas FPGAs e suas características                                | 24          |

## Acrónimos e Unidades

| Acrónimo | Significado                                                 |  |  |

|----------|-------------------------------------------------------------|--|--|

| AMBA     | Advanced Microcontroller Bus Architecture                   |  |  |

| AMS      | Analog Mixed Signal                                         |  |  |

| AP       | All Programmable                                            |  |  |

| APIX     | Automotive Pixel Link                                       |  |  |

| ARM      | Acorn RISC Machine, posteriormente Advanced RISC Machine    |  |  |

| ASIC     | Application Specific Integrated Circuit                     |  |  |

| AXI      | Advanced eXtensible Interface                               |  |  |

| BOM      | Bill of Materials                                           |  |  |

| BSP      | Board Support Package                                       |  |  |

| CAN      | Controller Area Network                                     |  |  |

| CCD      | Charge-Coupled Device                                       |  |  |

| CD       | Compact Disc                                                |  |  |

| CI / IC  | Circuito Integrado, Integrated Circuit                      |  |  |

| CMOS     | Complementary Metal-Oxide-Semiconductor                     |  |  |

| DAC      | Digital-to-Analog Converter                                 |  |  |

| DC       | Direct Current                                              |  |  |

| DDR      | Double Data Rate                                            |  |  |

| DEEC     | Departamento de Engenharia Electrotécnica e de Computadores |  |  |

| DMA      | Direct Memory Access                                        |  |  |

| (D)RAM   | (Dynamic) Random Access Memory                              |  |  |

| DRC      | Design Rule Check(ing)                                      |  |  |

| DSP      | Digital Signal Processor                                    |  |  |

| (EEP)ROM | (Electrically-Erasable Programmable) Read-Only Memory       |  |  |

| EMC      | Electromagnetic Compatibility                               |  |  |

| EOL      | End of Line                                                 |  |  |

| ESCL     | Electronic Steering Column Lock                             |  |  |

| FCTUC    | Faculdade de Ciências e Tecnologia da UC                    |  |  |

| FFC      | Flexible Flat Cable                                         |  |  |

| FIFO     | First In, First Out                                         |  |  |

| FMC      | FPGA Mezzanine Card                                         |  |  |

| FPC      | Flexible Printed Circuit                                    |  |  |

| FPD-Link | Flat Panel Display Link                                     |  |  |

| FPGA     | Field-Programmable Gate Arrays                              |  |  |

| FPS      | Frames Per Second                                           |  |  |

| GDC      | Graphics Display Controllers                                |  |  |

| GIP      | Graphic Interface Processor                                 |  |  |

| GND      | Ground                                                      |  |  |

| GP       | General Purpose                                             |  |  |

| GPIO     | General Purpose Input/Output                                |  |  |

| HDMI     | High-Definition Multimedia Interface                        |  |  |

| HP       | High Performance                                            |  |  |

HS-CAN High Speed CAN I/O Input/Output

I2C / IIC Inter-Integrated Circuit IP Intellectual Property

ISE Integrated Synthesis Environment,

(ferramenta de software produzida pela Xilinx)

ISO International Organization for Standardization

LCD Liquid-Crystal Display

LED Light-Emitting Diode

LIFO Last In. First Out

LIN Local Interconnect Network

LPC Low-Pin Count

LSB Least Significant Bit

LSD Laboratório de Sistemas Digitais

LTPS Low-Temperature Polycrystalline Silicon LVDS Low-Voltage Differential Signaling

MCU Microcontroller Unit

MIEEC Mestrado Integrado em Engenharia Electrotécnica e de Computadores

MMCM Mixed-Mode Clock Manager

MOST Media Oriented Systems Transport

MS-CAN Medium Speed CAN NGI **Next-Generation Interface PATS** Passive Anti-Theft System **PCB** Printed Circuit Board PLProgrammable Logic **PLL** Phase-Locked Loop Pmod Peripheral Modules PS **Processing System**

PSD Projecto de Sistemas Digitais PWM Pulse-Width Modulation RGB Red, Green and Blue

RISC Reduced Instruction Set Computing

ROI Region of Interest

RSDS Reduced Swing Differential Signal

RTL Register Transfer Level

SA Sociedade Anónima

SDK Software Davidopment

SDK Software Development Kit SMD Surface-Mount Device

SO / OS Sistema Operativo, Operating System

SoC System-on-a-Chip

SPI Serial Peripheral Interface SVF Software Validation Facility

TFT Thin-Film-Transistor

TTL Transistor-Transistor Logic

UART Universal Asynchronous Receiver/Transmitter

USB Universal Serial Bus

VCC Tensão de alimentação positiva

VCOM Common Voltage

| Video DMA                             |

|---------------------------------------|

| Video Graphics Array                  |

| VHSIC Hardware Description Language   |

| Very High Speed Integrated Circuits   |

| Vehicle Interface Processor           |

| Xilinx Analog-to-Digital Converter    |

| Zynq Evaluation and Development Board |

|                                       |

| Grandeza              | Unidade   | Símbolo  |

|-----------------------|-----------|----------|

| Comprimento           | metro     | m        |

| Corrente eléctrica    | ampere    | A        |

| Frequência            | hertz     | Hz       |

| Informação digital    | bit, byte | b, B     |

| Potencial elétrico    | volt      | V        |

| Resistência eléctrica | ohm       | $\Omega$ |

| Resolução             | píxel     | px       |

| Temperatura           | celsius   | °C       |

| Tempo                 | segundo   | S        |

### 1 Introdução

#### 1.1 Motivação

Os painéis de instrumentos usados em automóveis têm de ser bastante robustos em termos de segurança, já que deles podem inclusivamente depender a vida de pessoas. Têm de cumprir diversas normas e padrões internacionais, entre os quais a ISO 26262 [1] no que diz respeito à segurança funcional. É bastante importante testar este tipo de equipamentos de forma a confirmar a sua resposta em situações de possíveis falhas.

De forma a validar o seu comportamento, queríamos proceder à captura das imagens digitais que são enviadas para o ecrã do painel de instrumentos. Posteriormente estas imagens poderiam ser alvo de comparação com imagens de referência e, em caso de uma avaliação positiva, validaríamos assim o desempenho do equipamento.

Para tal, teria de recorrer a uma FPGA, já que era uma das restrições imposta pela empresa em que o projecto foi inserido, devido ao bom compromisso preço/desempenho que é espectável neste tipo de equipamentos quando aplicados a este tipo de problemas. Permitia ainda agilizar o processo de desenvolvimento e desenvolver uma solução adaptável e flexível.

Em termos pessoais, parte do interesse para desenvolver este trabalho passava pelas condições em que se ia realizar, ao tratar-se de um estágio a ser desenvolvido nas instalações da CRITICAL Software, num ambiente mais próximo do que poderei encontrar num futuro a curto prazo.

#### 1.2 Objetivos

O objectivo principal do trabalho passava por capturar as imagens que estão a ser enviadas para o ecrã do painel de instrumentos. Pretendia-se implementar uma solução que capturasse as imagens a serem enviadas para o ecrã, para posterior validação. O sistema deveria ser obrigatoriamente implementado numa FPGA. Deveria ser desenhada toda a arquitectura do sistema. Teria de ser desenvolvida toda a plataforma de *hardware*, assim como *software* adicional necessário para a configuração do *hardware*.

Para implementar o sistema por completo, em condições reais, era ainda necessário projectar a interface entre os equipamentos (FPGA, placa do painel de instrumentos e respectivo ecrã). Para o efeito teria de ser desenhada uma PCB.

Como objectivos adicionais, poderia ser implementada parte da fase de validação na FPGA ou serem estudados mecanismos de transferência das imagens capturadas para outro computador, para serem aí processadas.

#### 1.3 Estrutura da dissertação

Anteriormente a esta secção temos parte da introdução, onde são apresentadas a motivação para este trabalho e os seus objectivos.

No capítulo seguinte é abordado o estado da arte, onde são apresentados outros trabalhos desta área e as suas conclusões, e as principais contribuições deste trabalho, nessa perspectiva.

O terceiro capítulo corresponde à apresentação do painel de instrumentos, com base numa inspecção visual e na análise da documentação. Segue-se (capítulo 4) o estudo da interface com o ecrã e a apresentação, já no capítulo subsequente (capítulo 5), dos factores que levaram à escolha da FPGA que viria a ser adquirida para dar continuidade ao projecto.

Numa outra parte é apresentada a arquitectura do sistema (capítulo 6) que pretendíamos implementar dividida em duas partes: arquitectura da parte "física" onde são apresentadas as possibilidades quanto à ligação dos equipamentos e a arquitectura do caminho de dados onde é exposto o *datapath* que foi idealizado para este projecto.

Segue-se o capítulo onde é descrita a implementação do sistema na FPGA (capítulo 7): começa por uma introdução ao Vivado da Xilinx, são mostrados mais alguns detalhes da implementação da plataforma de *hardware* e do *software* criado para essa plataforma, surgem algumas notas sobre o trabalho realizado na elaboração dos módulos iniciais, sucedendo-se a explicação dos testes realizados.

Posteriormente, é apresentado o projecto da PCB de interface, surgindo depois a secção onde é apresentado o sistema completo, com a ligação de todos os equipamentos (capítulo 0). Na fase final surgem algumas referências relativamente ao trabalho complementar que foi desenvolvido que incluem outros módulos que foram criados e possíveis melhoramentos (envio de informação para outras máquinas, possibilidades de multiprocessamento assimétrico, uso das interfaces Pmod e/ou saídas de vídeo, terminado com a apresentação de projectos de PCBs alternativas).

Para terminar, surgem as conclusões deste trabalho onde são expostas as notas finais sobre o mesmo, o que foi feito e o que pode ainda vir a ser desenvolvido de forma a dar continuidade a este projecto.

Informação complementar relativa ao trabalho desenvolvido pode ser encontrado nos anexos incluídos no final desta dissertação.

### 2 Estado da arte

É possível encontrar uma quantidade significativa de trabalhos científicos com objectivos semelhantes com alguma pesquisa. Por objectivos semelhantes, foi considerada a captura e/ou processamento de imagens com recurso a FPGAs independentemente da proveniência dos dados [2, 3, 4, 5, 6, 7, 8, 9, 10, 11], [12, 13, 14, 15, 16, 17, 18, 19, 20, 21] e [22, 23].

Embora não tenham sido encontrados grandes detalhes sobre a implementação destes projectos, a descrição das vantagens acaba por ser semelhante em todos eles. Alguns destes estudos afirmam que é possível fazer a captura de imagens em tempo-real com recurso exclusivo a FPGAs, noutros a FPGA surge como um complemento ao sistema permitindo assim aceleração por hardware, sendo depois as imagens processadas por DSPs (<u>Digital Signal Processor</u>) ou por outros processadores. A maioria refere as seguintes características como benefícios que o uso de FPGAs acrescenta aos seus projectos: a flexibilidade deste tipo de equipamentos é, por norma, mencionada como uma vantagem, ao permitir uma prototipagem mais rápida e com menos custos, podendo normalmente ser adaptada consoante os restantes equipamentos do qual provêm as imagens (com a nota de que, na maior parte dos projectos, as imagens provêm de câmaras/sensores de imagem (CCD ou CMOS)). Por vezes são também referidas as capacidades de portabilidade da solução, a sua escalabilidade ou possibilidade de expansão, e os baixos consumos energéticos.

Nalgumas das ligações incluídas nas referências é também possível aceder a outros projectos semelhantes nas citações ou, no caso inverso, trabalhos em que o projecto é citado.

Numa perspectiva um pouco diferente, foram encontradas algumas referências, principalmente dentro da oferta dos principais fabricantes, em que as FPGAs são consideradas como a alternativa a seguir no controlo e criação da própria interface gráfica destes painéis de instrumentos para automóveis [24, 25, 26, 27, 28, 29]. Mais uma vez são salientadas as potencialidades que este tipo de tecnologia pode providenciar: flexibilidade, redução dos custos e dos tempos de desenvolvimento entre outras.

#### 2.1 Principais contribuições

O trabalho desenvolvido surge de certa forma em linha com alguns dos trabalhos encontrados na pesquisa realizada para a elaboração do estado da arte. É possível afirmar que a captura de imagens em tempo-real com recurso a FPGAs é viável, independentemente da origem dos dados, com as devidas adaptações a este caso específico.

Ficaram também comprovadas as capacidades deste tipo de equipamentos no que diz respeito à sua flexibilidade, às possibilidades de reutilização de código/componentes que permitem tempos de desenvolvimento mais reduzidos, diminuição de custos e exportação para outras plataformas.

A escalabilidade do projecto também é viável uma vez que o equipamento utilizado ainda possuía muitos recursos disponíveis e possibilidades que não foram exploradas por completo. Estes recursos podem vir a ser utilizados para atingir os objectivos adicionais tais como a validação das imagens capturadas, feita na própria FPGA, ou a implementação do envio das imagens para outra máquina, com o mesmo objectivo de validação.

A principal singularidade do trabalho acaba por ser a aplicação a que se destina, à captura de imagens provenientes de um painel de instrumentos de automóvel com propósitos de validação. Esta acaba por se tornar a principal distinção relativamente aos restantes trabalhos e poderá inclusivamente tornar-se numa vantagem competitiva para as empresas em que este trabalho foi inserido.

### 3 Painel de instrumentos

A exposição do trabalho desenvolvido irá começar por uma análise do painel de instrumentos fornecido, talvez o principal elemento de todo este estudo.

Todo o equipamento é protegido por um corpo de plástico, sendo que na parte frontal, o plástico é côncavo e transparente permitindo a visibilidade de um ecrã (Fig. 1 - A1) que ocupa a grande maioria da sua extensão e ainda quatro elementos situados nas laterais do ecrã (dois de cada lado) (Fig. 1 - A2): dois sensores ópticos que permitem ajustar a luminosidade do ecrã em função da luz ambiente e dois indicadores, iluminados por LEDs, de avaria no *Airbag* e do sistema de segurança PATS (<u>Passive Anti-Theft System</u>). Destes elementos destaca-se o ecrã, sobre o qual recai o objectivo do trabalho: a captura das imagens que estão a ser emitidas.

Figura 1 - Fotografia do painel de instrumentos (frente)

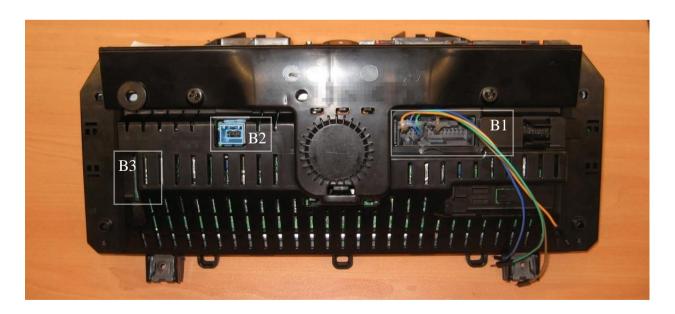

As restantes partes são de plástico preto, com os encaixes que permitem a montagem do painel no veículo, e tem gravadas as referências do produto e as logomarcas dos construtores automóveis (que foram dissimuladas na Figura 2 para que não possam ser identificadas).

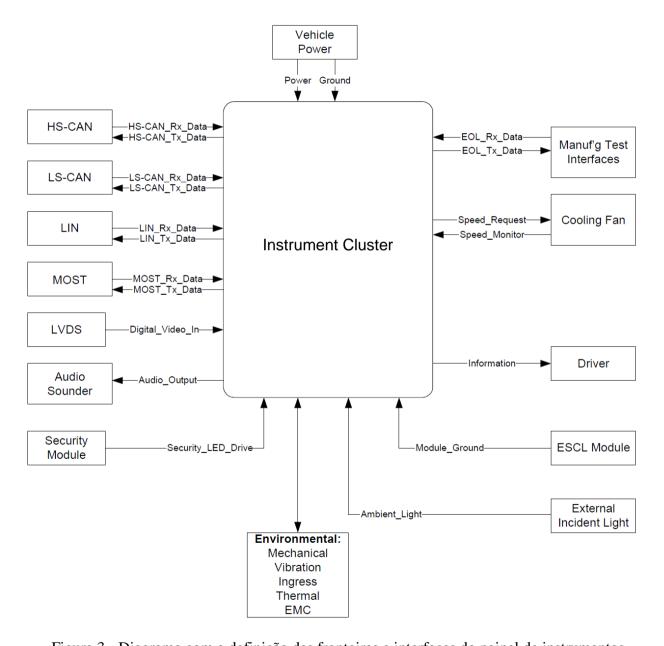

Imediatamente atrás do ecrã encontra-se exposto um altifalante que permitirá emitir avisos sonoros ao condutor (Fig. 5 - A3) e na parte traseira conseguimos distinguir três conectores (Fig. 2 - B1, B2 e B3), estando um deles colocado de forma lateral (Fig. 2 - B3): orientado para a lateral do painel de instrumentos temos um conector MOST (*Media Oriented Systems Transport*) (Fig. 2 - B3) para a ligação com equipamentos multimédia (navegação, *infotainment*, telemóvel, etc.), existe também um conector LVDS (*Low-Voltage Differential Signaling*) (Fig. 2 - B2) que permite a entrada de um sinal de vídeo externo e por último mas de substancial relevância temos o conector principal do painel de instrumentos (Fig. 2 - B1) que implementa todas as principais comunicações com os restantes equipamentos do veículo (essencialmente via CAN e LIN) assim como a alimentação do próprio painel.

Para além de disponibilizar os pinos para as comunicações CAN, LIN e alimentação, temos ainda linhas para alimentação e regulação de uma possível ventoinha para efeitos de dissipação do calor gerado pelos CI que não se encontra montada no modelo disponibilizado (se bem que é facilmente perceptível qual seria a sua posição no painel), linhas para a transmissão dos sinais de teste (a realizar no final da linha de produção) identificadas como EOL (*End of Line*) assim como pinos para o bloqueio da coluna de direcção do veículo (ESCL - *Electronic Steering Column Lock*).

Figura 2 - Fotografia do painel de instrumentos (trás)

Para efeitos deste trabalho, foram apenas utilizadas as ligações com os *jumper cables*, sendo que, como referido no parágrafo anterior, um par se destina a alimentação de todo o painel e o outro à ligação CAN de alta velocidade (também essencial para que o painel inicie o seu funcionamento, permitindo também enviar mensagens que alterem a resposta do sistema e, consequentemente, as imagens apresentadas no ecrã).

Para completar e clarificar o que acabou de ser escrito, foi acrescentado o seguinte diagrama, presente na documentação fornecida, onde são apresentadas as diversas interfaces de entrada e saída do painel de instrumentos.

Figura 3 - Diagrama com a definição das fronteiras e interfaces do painel de instrumentos

Prossigamos a análise para o interior do painel de instrumentos. Para expor a placa principal do painel é necessário separar o corpo de plástico em duas partes. Deparamo-nos com uma quantidade significativa de circuitos integrados e elementos passivos. Apenas foram inspecionados os componentes montados na face exposta da PCB, uma vez que não foi possível desaparafusar manualmente a placa do seu suporte metálico. Ainda assim, foram certamente analisados os componentes principais, que necessitam de estar na face visível por motivos de espaço e de dissipação de calor.

Figura 4 - Fotografia com a placa do painel de instrumentos

Para além dos três conectores anteriormente referidos, que servem de ligação com equipamento exterior ao painel de instrumentos conseguimos agora ver cinco conectores adicionais para ligar os diferentes elementos do painel de instrumentos, dois para ligar a PCB principal aos componentes nas laterais do ecrã (Fig. 5 - A2), dois para a ligação com o ecrã (Fig. 5 - A1) e o último para a conexão com o altifalante (Fig. 5 - A3).

Atendendo à perceptível importância que as ligações da placa principal com o ecrã iriam ter neste trabalho, foi nestas que se concentraram as primeiras tarefas desenvolvidas. Ainda relativamente a estas, o conector maior (e respectiva fita) apresentava-se, presumivelmente, como sendo responsável pela transmissão dos dados e dos sinais de sincronismo para o ecrã sendo que o outro teria a seu cargo funções secundárias, como a alimentação dos LEDs (*Light-Emitting Diode* - Díodo Emissor de Luz) de retroiluminação do ecrã, já que o mesmo acontece em equipamentos semelhantes.

Embora não tenha sido possível aceder ao desenho ou esquemático da placa, nem à lista dos materiais, foi feito o levantamento dos principais CIs montados na PCB, na espectativa de perceber um pouco melhor a função de cada um e o funcionamento geral do painel de instrumentos.

Figura 5 - Fotografia com a placa do painel de instrumentos (com anotações)

Figura 6 - Esquema mais detalhado das interfaces entre componentes do painel de instrumentos e/ou restantes elementos do veículo

É possível cruzar a notação da Figura 5 com o diagrama da Figura 6, onde o painel de instrumentos é apresentado com algum detalhe adicional, sendo agora visíveis (de forma esquemática) alguns dos componentes que fazem parte do painel assim como as ligações que existem entre os mesmos.

O esquema foi adaptado de um que se encontra na documentação do painel de instrumentos [30] e que aparenta referir-se à próxima geração de interfaces (mencionada como NGI (*Next-Generation Interface*) e que já apresenta uma série de componentes diferentes dos que constituem o modelo disponibilizado. É possível identificar dois dos componentes principais, designados como o VIP (*Vehicle Interface Processor*) e o GIP (*Graphic Interface Processor*). O VIP é o microcontrolador TMS470 da Texas Instruments, responsável pela maior parte das interfaces (CAN, LIN, etc.) do painel de instrumentos com os restantes equipamentos do veículo e o GIP é o Fujitsu MB86R01 Graphics SoC (*System on a Chip*) "Jade" responsável pelo controlo da parte gráfica do painel.

Além destes elementos temos ainda de destacar a referência ao ecrã TFT-LCD, pelo facto de ser neste diagrama que surge pela primeira vez a alusão à profundidade de cor do mesmo, RGB666 que se traduz na utilização de 6 *bits* para a representação de cada uma das cores primárias aditivas RGB (*Red*, *Green and Blue* - Vermelho, Verde e Azul) que resulta na utilização de 18 *bits* no total por cada *pixel* da imagem do ecrã. São também mencionadas algumas das caraterísticas previamente referidas: 12.3 polegadas de diagonal, num formato 8:3, e uma resolução de 1280 por 480 pixéis. Aparecem ainda destacadas as tensões necessárias na alimentação do ecrã LCD (+8V, +6V, -8V, -6V e -12V) que poderiam limitar ou influenciar a FPGA a escolher caso fosse necessário receber ou fazer o controlo "directo" (sem condicionamento) destes sinais.

Foi ainda acrescentada a parte do esquemático relacionada com a entrada de vídeo LVDS, que passa pelo *Deserializer* da National Semiconductor (DS90UR124) e pela FPGA Lattice (A307RRF8) para a conversão do espaço de cor antes de entrar no GIP. Tudo isto foi aferido com base a breves referências na documentação do painel de instrumentos [30].

Para além da análise feita por inspecção visual, o estudo relativo ao painel de instrumentos baseou-se também na documentação disponibilizada, e da qual foram retirados e adaptados alguns dos esquemas apresentados [31], contudo, a informação fornecida encontrava-se por vezes limitada por questões de confidencialidade e/ou segredo industrial. Da documentação é possível retirar informações importantes como a resolução (2XVGA de 1280 pixéis horizontais e 480 verticais), o *aspect ratio* (proporção da tela) (8:3) e a dimensão (12.3" de diagonal do ecrã, com uma área activa de 291.84 mm por 109.44 mm).

Fica ainda aqui uma nota relativa à resolução do ecrã identificada como 2XVGA ([32], [33] e [34]). Depreende-se, devido à escassez de referências, que se trata de uma resolução pouco comum e fora dos vários *standard* VGA (*Video Graphics Array*) e suas extensões. Tal poderá dever-se ao facto de a proporção da tela (8:3) ser algo incomum mesmo para ecrãs de tamanho mais amplo (*wide*) que são geralmente de formato 16:9.

## 4 Ligação com o ecrã

Neste capítulo pretende-se dar conta do trabalho de pesquisa desenvolvido para obter uma melhor compreensão sobre a interface do painel de instrumentos com o ecrã LCD. Eram necessárias mais informações para além das características já anotadas neste documento (resolução, proporções e dimensões). Assim, começou-se novamente por uma análise visual do equipamento, na procura de alguma referência ou outras informações que pudessem úteis cruzando-as posteriormente com os detalhes apresentados na documentação. Analisando a fita principal que liga o ecrã à placa principal do painel de instrumentos podemos verificar, de forma quase imediata, duas particularidades: A primeira é de que estamos perante um circuito impresso flexível (FPC - *Elexible Printed Circuit*) e não apenas uma simples fita de ligação; a segunda é que a disposição das "linhas" de ligação e da preocupação de aproximar algumas delas a dado ponto sugere que os sinais possam estar a ser transmitidos em pares diferenciais (em "acoplamento apertado" (tight coupling)).

É praticamente possível distinguir as linhas de sinais de dados, de relógio e sincronismo, alimentação e massa (*ground*) olhando para a sua espessura e disposição das mesmas, sendo que as primeiras (dados, relógio e sinc.) são as mais estreitas (é mesmo possível verificar que linhas de massa consecutivas se encontram todas elas ligadas, formando um pequeno "plano" ao mesmo potencial enquanto as outras (não consecutivas) acabam por ser as linhas mais largas de forma a isolar melhor as restantes).

Relativamente à fita secundária, as linhas são todas idênticas e não dá para aferir muito mais a partir da aparência da mesma. Mantinha-se a convicção de que esta ligação se destinava a funções secundárias do ecrã, em especial para a alimentação dos LEDs de retroiluminação.

Em termos visuais não foi possível analisar melhor estes circuitos uma vez que depois acabam por passar por debaixo do dissipador de calor que se encontra tanto aparafusado como colado à restante estrutura e que não foi retirado de forma a não danificar o equipamento.

Figura 7 - Foto do FPC principal do ecrã

Ao retirar a placa do painel de instrumentos e o seu suporte metálico, revelam-se as referências do ecrã.

A partir da *datasheet* do ecrã LCD [31], confirma-se a maior parte das informações entretanto recolhidas: estamos perante um ecrã de 12.3", 8:3 de 1280x480 pixéis RGB666 e cuja interface é feita através de dois FPCs, um de 50 pinos e 0.5mm de espaçamento entre pinos (*pitch*) para o painel propriamente dito e outro de 20 pinos com o mesmo *pitch* para a retroiluminação (*backlight*).

Ainda, desta mesma documentação, percebe-se que é possível configurar o ecrã através de uma comunicação SPI (<u>Serial Peripheral Interface</u>) e temos também informação sobre medidas e detalhes construtivos. Depois, de relevante, temos acesso às tabelas de "atribuição de pinos" (*pin assignment*) de ambos os FPC, sugerindo também os conectores que devem ser usados para a ligação (série 9687S da IRISO).

Temos a informação completa sobre o FPC de 50 pinos e quais os pinos dedicados à alimentação do ecrã, massa (*ground* (GND)), comunicação SPI, dados sobre a cor de cada *pixel*,

relógio e sincronismo entre outros (teste e selecção de modo de funcionamento) que define se o ecrã se encontra a funcionar em modo RSDS (<u>Reduced Swing Differential Signal</u>) ou modo TTL (<u>Transistor-Transistor Logic</u>) (<u>single-ended signaling</u>)) apresentando posteriormente a informação análoga para o FPC de 20 pinos.

Legenda e notas:

#### Alimentação

Tensões potencialmente perigosas Usado para para FPGAS, abaixo de 0V e acima de controlador do ecrã. 3.3V (ou 5V). Poderia ser intere

#### Dados da cor e sinais de sincronismo

Informação crucial para o sistema que pretendíamos implementar.

### Comunicação SPI

Usado para configuração do controlador do ecrã

Poderia ser interessante "interceptar" para determinar alguns parâmetros de configuração do ecrã.

Figura 8 - Foto do FPC principal do ecrã (com anotações)

A confirmação relativa ao modo de funcionamento do ecrã só poderia vir a ser esclarecida determinando o valor do sinal do pino "TR" com recurso a um osciloscópio ou criando um circuito digital de teste na FPGA, sendo que as notas presentes na *datasheet* do ecrã apontam no sentido de os sinais estarem a ser transmitidos em modo TTL (*single-ended*) e não de forma diferencial uma vez que indicam que as informações sobre o modo RSDS são apenas para referência e que seriam necessários alguns testes e alterações nas instalações de produção. Segundo o fabricante, a interface do ecrã tanto poderá ser configurada para funcionar em modo LVDS/RSDS ou TTL, consoante os requisitos do sistema (embora a versão parcial da *datasheet*, disponibilizada pelo fabricante, apenas referisse o modo TTL). De forma a precaver ambas as situações seria importante escolher uma FPGA que pudesse lidar com ambos os tipos de sinal.

No *datasheet* destaca-se ainda a informação relativa ao valor recomendado de VCC ser 3.3V o que faz com que o valor máximo para os sinais SPI, os dados, sinais de sincronismo e relógio esteja limitado por este valor, sendo que os restantes valores variam entre -12V a 8V), consumos de corrente, etc. [31].

Temos ainda os diagramas temporais relativos à transmissão de dados nos diversos modos que são também eles muito importantes de forma a sincronizar a informação que pretendo receber, permitindo também desprezar os dados enviados nos períodos de *blanking*, acompanhada por uma tabela com todos os parâmetros temporais entre os quais se deve realçar a frequência do sinal de relógio (41.34MHz) e a "frequência vertical" (58.71Hz aproximadamente 60Hz que é o padrão neste tipo de equipamentos uma vez que se traduz numa "cadência" de *frames* (*frame rate*) de 60FPS (*Frames Per Second*)) [31].

Tanto os valores de tensões eléctricas dos sinais, como a sua frequência máxima tiveram influência na definição dos requisitos para a FPGA, assim como no projecto da interface entre os sistemas.

No final temos outras informações, como as sequências necessárias para ligar e desligar o ecrã de forma correcta, uma tabela que faz corresponder a algumas cores a respectiva combinação RGB, os procedimentos para detecção de falhas e funções de autoprotecção, dados sobre as caraterísticas ópticas aos quais se sucedem as informações sobre a comunicação SPI que podem assumir alguma importância caso quiséssemos capturar estes sinais usando a FPGA e ficar assim com acesso completo às configurações do ecrã, terminando com alguma informação complementar sobre a luminância ao longo do tempo de vida do ecrã, testes ambientais e de fiabilidade, requisitos de qualidade, etc. [31].

## 5 Escolha da FPGA

A escolha da FPGA que servisse os propósitos do presente trabalho deveria cumprir os seguintes requisitos:

- (i) a FPGA tem de disponibilizar pinos de entrada/saída (I/O <u>Input/Output</u>) suficientes para capturar, pelo menos, os sinais de dados, sincronismo e de relógio do sinal de vídeo a ser enviado para o ecrã (tendo ainda em conta a frequência dos mesmos, devendo precaver também a possibilidade de estes sinais estarem a ser transmitidos em pares diferenciais);

- (ii) a FPGA tem também de ter uma memória externa RAM (<u>Random Access Memory</u>) de 512MB a 1GB de forma a conseguir armazenar alguns dos *frames* que fossem enviados para o ecrã;

- (iii) a FPGA deve ter além da parte de lógica programável (PL <u>Programmable Logic</u>), característica comum a todas as FPGAs, um outro processador <u>hard-core</u> (processador ARM (<u>Acorn RISC (Reduced Instruction Set Computing) Machine</u>, posteriormente <u>Advanced RISC Machine</u>), por exemplo) de forma a ter mais possibilidades de processamento e executar acções paralelamente às implementadas na parte de PL;

- (iv) necessita ainda de um conector de alta-densidade de pinos (e, consequentemente, *pitch* baixo) de forma a ser possível fazer todas as ligações necessárias num espaço reduzido;

- (v) ter uma ter interface USB (<u>Universal Serial Bus</u>) (2.0 ou 3.0) ou Gigabit Ethernet para que possa cumprir com objetivos adicionais, ao enviar os *frames* para outro computador para posterior processamento (como a SVF <u>Software Validation Facility</u>, disponível na CRITICAL) com uma cadência suficientemente rápida completando assim a parte de captura de imagens;

- (vi) e por fim as ferramentas de desenvolvimento e suporte deveriam, obrigatoriamente, ser gratuitas.

Foram procurados equipamentos que cumprissem com os requisitos apresentados dentro da oferta dos principais fabricantes de FPGAs, a Altera e a Xilinx. Por recomendação de engenheiros mais seniores da CRITICAL Software foi aconselhada a escolha de uma FPGA da Xilinx devido a experiências positivas que tiveram com produtos desta marca e com as suas ferramentas de desenvolvimento, para além de ser a empresa líder do mercado das FPGAs. De todas as opções consideradas houve uma que se destacou, a placa ZedBoard, ao cumprir com todos os parâmetros enunciados ao preço mais competitivo e incluir uma das soluções mais avançadas que a Xilinx disponibiliza de momento, um SoC (*System-on-a-Chip*) Zynq-7000.

Na tabela 1 são apresentadas as FPGAs que foram alvo de pesquisa para a realização do presente trabalho.

Tabela 1 - Lista de algumas FPGAs e suas caractrísticas

| Nome                                                          | Preço   | RAM   | Proc. h. c. | USB | GbE | Exp. a. d.  | IDE    |

|---------------------------------------------------------------|---------|-------|-------------|-----|-----|-------------|--------|

| Nexys2 Spartan-3E FPGA Board                                  | \$200   | 16MB  | x           | ✓   | ×   | Hirose FX2  | ISE    |

| Nexys3 Spartan-6 FPGA Board                                   | \$270   | 16MB  | x           | ✓   | ✓   | VHDC        | ISE    |

| Spartan 3E Starter Board                                      | \$299   | 64MB  | ×           | ×   | ×   | Hirose FX2  | ISE    |

| Nexys4 Artix-7 FPGA Board                                     | \$320   | 16MB  | x           | ✓   | ✓   | x           | ISE    |

| ZedBoard Zynq-7000 Development Board                          | \$395   | 512MB | ✓           | ✓   | ✓   | FMC - LPC   | Vivado |

| Atlys Spartan-6 FPGA Development Board                        | \$419   | 256MB | ×           | ✓   | ✓   | VHDC        | ISE    |

| Xilinx Zynq-7000 All Programmable SoC<br>ZC702 Evaluation Kit | \$895   | 1GB   | ✓           | ✓   | ✓   | 2xFMC - LPC | Vivado |

| Genesys Virtex-5 FPGA Development Board                       | \$1 099 | 128MB | ×           | ✓   | ✓   | 2xVHDC      | ISE    |

| Xilinx Artix-7 FPGA AC701 Evaluation Kit                      | \$1 295 | 1GB   | ×           | ✓   | ✓   | FMC-HPC     | Vivado |

| Xilinx Kintex UltraScale FPGA KCU105<br>Evaluation Kit        | \$2 495 | 2GB   | ×           | ✓   | ✓   | FMC-HPC     | Vivado |

A ZedBoard resulta de uma parceria entre a Xilinx, a Avnet e a Digilent para reduzir os custos de produção e distribuição e torná-la assim mais acessível ao público. Possuí também um *site* e comunidade próprios (provavelmente a comunidade mais vasta dentro desta categoria de produtos) tornando-se assim mais fácil de aceder a suporte técnico, documentação, projectos de referência e fórum de discussão [35].

## 6 Arquitectura

Muito do trabalho que aqui será descrito influenciou, de certa forma, a escolha do material necessário para o desenvolvimento deste trabalho. Contudo, só depois de escolhida e encomendada a FPGA é que se poderia definir por completo a arquitectura do sistema que se pretendia implementar.

Podemos separar a definição da arquitectura do sistema em duas partes distintas: uma "física" onde definimos a forma como iríamos ligar "electromecanicamente" os sistemas (PCB do painel de instrumentos, ecrã e FPGA) e outra que se prende com um funcionamento do sistema do ponto de vista da programação da FPGA, com a definição do caminho de dados.

## 6.1 Arquitectura física

Relativamente à parte física, era agora possível, cruzando as informações sobre a FPGA adquirida e o ecrã LCD, definir quais os tipos de conectores e cabos de que iriam ser necessários para efectuar as ligações. A FPGA disponibiliza três tipos de conectores de expansão, expondo pinos de entrada/saída (I/O):

• 1 Conector FMC (<u>FPGA Mezzanine Card</u>) LPC (<u>Low-Pin Count</u>) que expõe 68 pinos de I/O digitais quando configurados no modo <u>single-ended</u>, podendo também ser configurados como 34 pares diferenciais. No caso da Zedboard estes pinos são alimentados por uma tensão variável definida por um <u>jumper</u> na placa (pode alternar entre 1.8V, 2.5V ou 3.3V) [36]

- 5 Conectores compatíveis com Digilent Pmod<sup>TM</sup> (<u>Peripheral Mod</u>ules) (2x6) cada um expondo 8 pinos de I/O (mais 2 pinos de alimentação 3.3V e 2 de massa), sendo que um se encontra ligado directamente ao processador ARM (PS <u>Processing System</u>) enquanto os restantes quatro permitem interface com a lógica programável (PL) do Zynq-7000 AP (<u>All Programmable</u>) SoC. Apenas dois destes suportam pares diferenciais.

- 1 Conector AMS (<u>Analog Mixed Signal</u>) ou XADC (<u>Xilinx Analog-to-Digital Converter</u>) que permite a entrada de alguns sinais tanto digitais como analógicos.

(Informação adicional pode ser consultada em [37], págs. 21 a 25)

Optou-se pela ligação FMC por se tratar da interface de expansão principal, uma vez que providência um maior número de pinos de I/O, suportando a interface com pares diferenciais, não colocando portanto nenhum entrave à ligação com o ecrã, neste aspecto. Permite também desenhar uma solução mais compacta em termos de espaço já que este conector apresenta uma maior densidade de pinos quando comparado com os conectores Pmod que são mais indicados para outro tipo de periféricos (que por norma necessitam de menos pinos de I/O). <sup>1</sup>

Existia desde início a necessidade de fazer uma PCB (em alternativa poderia ser desenhado um FPC, mas, neste caso, tal não se justificava e representaria custos adicionais) para tratar da interface entre os três sistemas referidos (PCB do *painel de instrumentos*, ecrã e FPGA) e, escolhida a interface de expansão da FPGA a utilizar, estavam definidos os conectores de que iríamos precisar de montar nesta placa. Seriam necessários 3 conectores: um conector FMC LPC "macho" para a ligação com a FPGA, e dois conectores FFC (*Flexible Flat Cable*)/FPC de 50 pinos (da série IRISO 9687S ou compatível) para a ligação com a PCB do *painel de instrumentos* e com o ecrã. Seria também indispensável uma fita FFC de 50 pinos de forma a ligar a PCB do painel de instrumentos com a PCB que iríamos projectar (esta fita deveria ter, de preferência, os mesmos entalhes (*notches*) que o FPC do ecrã apresenta (Figura 7) de forma a que o encaixe seja mais seguro.

<sup>&</sup>lt;sup>1</sup> Podemos encontrar alguns exemplos de periféricos de expansão já existentes que utilizam a interface FMC ou Pmod nas seguintes ligações (FMC [51], Pmod [52])

Para a arquitectura física do nosso sistema foram consideradas as seguintes alternativas:

• Uma ligação da FPGA seria ligada em paralelo com o ecrã criando como que uma derivação (em "T") nas linhas de relógio, dados, e sincronismo, para que estas entrassem directamente tanto no ecrã como na FPGA (Fig. 9).

Figura 9 - Ilustração da primeira hipótese de arquitectura física

Receber os sinais a serem enviados pelo painel de instrumentos na FPGA, em

determinados pinos de I/O a definir (a funcionarem como entradas) e replicar os

sinais recebidos noutros pinos distintos (que seriam definidos como saídas)

enviando-os para o ecrã. Os três sistemas seriam ligados em série de acordo com a

seguinte ordem: Painel de Instrumentos → FPGA → Ecrã (Fig. 10).

Figura 10 - Ilustração da segunda alternativa de arquitectura física

A decisão recaiu sobre a segunda opção uma vez que, na primeira, a impedância das linhas de entrada pode ser alterada significativamente, já que os sistemas se encontrariam ligados em paralelo, o que poderia comprometer a integridade destes sinais. A segunda alternativa pretende compensar este aspecto negativo mas em contrapartida irá necessitar de utilizar o dobro dos pinos de entrada/saída: a primeira metade irá servir como pinos de entrada (tal como na primeira opção) e a segunda como pinos de saída de sinais.

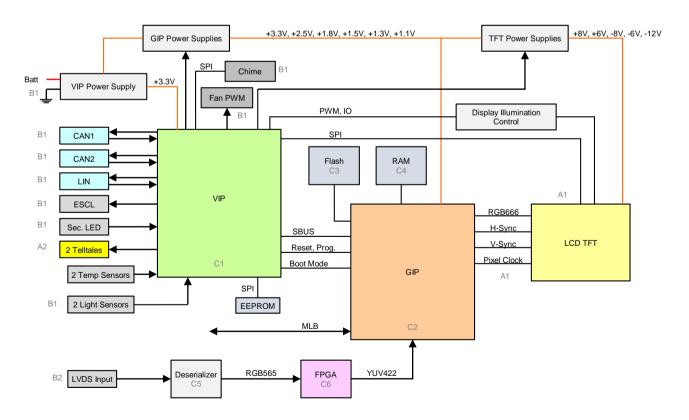

## 6.2 Arquitectura do caminho de dados (datapath)

A arquitectura do caminho de dados foi, inicialmente, definida de forma conceptual, para que servisse, posteriormente, de referência para implementação na FPGA. Deve-se referir que a maior parte das decisões tomadas, relativamente a esta arquitectura, assim como à arquitectura física apresentada na secção anterior, tiveram por base o que foi discutido em algumas reuniões com engenheiros seniores da CRITICAL Software e acabam por transpor para o papel muitas das suas sugestões para este trabalho. Segue-se apresentação da arquitectura do sistema.

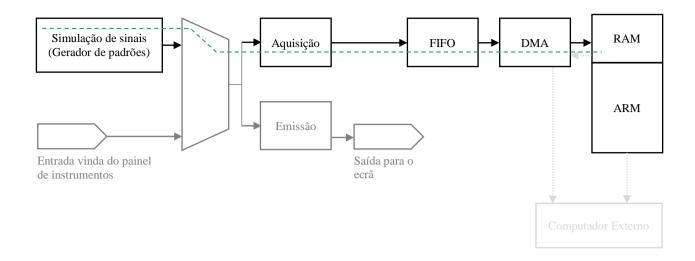

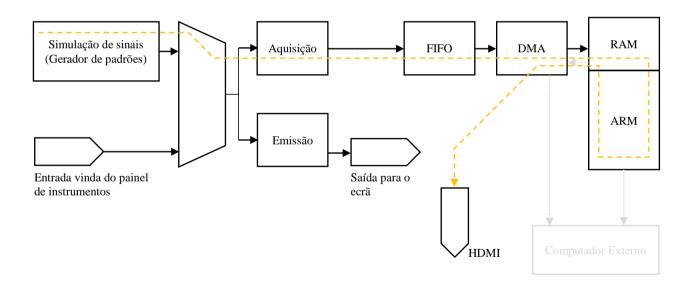

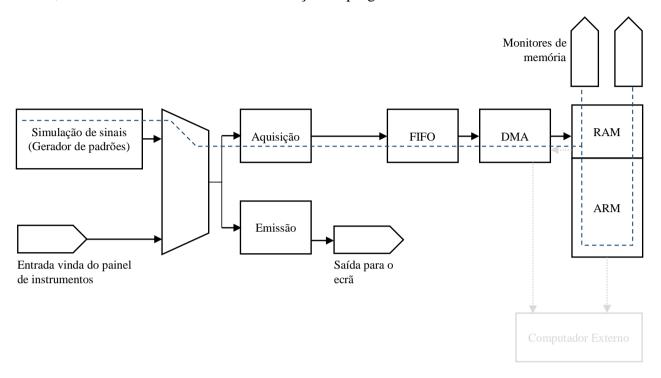

Figura 11 - Diagrama de blocos da arquitectura do caminho de dados

O sistema deve, antes de mais, permitir alternar entre a captura de imagens vindas da placa do painel de instrumentos ou das imagens vindas de um simulador (gerador) de sinais implementado na FPGA que permita a geração de padrões para efeitos de teste do sistema. Os sinais passariam por dois caminhos distintos: um que se limitava a emitir os sinais para o ecrã do painel de instrumentos, para que continuassem a aparecer neste ecrã, enquanto o segundo trata da aquisição dos sinais de forma a passá-los para a memória da FPGA. Como os sistemas funcionam a diferentes frequências de relógio, é praticamente imperativo que nesta parte de aquisição das imagens fosse usado um *buffer* FIFO (*First In, First Qut*) [38] de forma a lidar com esta situação, sendo que a parte de entrada funcionaria à frequência de relógio do ecrã e a parte de saída poderá funcionar às frequências permitidas pela FPGA, podendo ainda acumular temporariamente algumas amostras em caso de possíveis paragens (*stall*) causadas por indisponibilidade dos recursos a que pretendemos aceder (p. ex. acessos concorrentes à memória) guardando-as até que estas possam prosseguir pelo restante caminho de dados (*datapath*).

Posteriormente, pretende-se enviar os dados recebidos para a RAM existente na placa ZedBoard (512MB DDR3) em detrimento da possibilidade de usar BRAM (*Block RAM*) disponíveis no "tecido" de lógica programável (PL) da FPGA (140 blocos de 36Kb cada, 560KB no total, de acordo com [39] (a versão do SoC Zynq-7000 que a ZedBoard disponibiliza é a Z-7020, Package CLG484)) para criar uma memória nesta região, poupando-os para os restantes elementos necessários ao *datapath*. Esta opção foi tomada já que, mesmo usando todos os blocos BRAM disponíveis para criar uma memória, estes seriam, ainda assim, insuficientes para armazenar uma única imagem do fluxo de vídeo que está a ser enviado para o ecrã (1350 kB por *frame*, ver expressão (1)), não considerando possibilidades de compressão ou redução do espaço de cor da imagem que vão contra os objectivos do trabalho, onde se inclui a preservação total das imagens e de toda a informação que estas representam.

$$\frac{n^{\circ} \text{ de bytes úteis}}{frame} = 1280 \times 480 \left(\frac{\text{píxeis}}{frame}\right) \times 18 \left(\frac{bits}{\text{píxeis}}\right) =$$

$$= 11059200 \frac{bits}{frame} = 1350 \frac{\text{kB}}{frame}$$

(1)

Uma solução que fizesse apenas uso dos blocos BRAM poderia trazer vantagens em termos de desempenho (do ponto de vista temporal) em detrimento da possibilidade de armazenar imagens completas. Poderia ser interessante num projecto de integração da FPGA com outros computadores em que o armazenamento das imagens poderia ser parcial (limitado a algumas linhas da imagem) e os dados fossem enviados para outra máquina para um armazenamento mais completo e efectivo e para posterior processamento. Esta solução surge na linha daquilo que se pretende como possível evolução e/ou desenvolvimento deste trabalho.

Neste trabalho o sistema foi abordado numa perspectiva em que deveria funcionar de forma isolada (*stand-alone*) e para tal deveria armazenar imagens completas. Assim é impreterivelmente necessário recorrer à memória RAM da placa e a mecanismos de DMA (*Direct Memory Access*) de forma a libertar o processador ARM (*dual-core*) da maioria do "peso" deste procedimento [40]. Uma vez na RAM os dados estarão também acessíveis pelo processador ARM. Aí é possível proceder a posterior processamento ou enviá-los para outra máquina com o mesmo intuito, por USB ou via Ethernet, (linha a azul - Figura 11) sendo que esta tarefa também poderia ser desempenhada por módulos implementados na FPGA (PL) (linha a verde - Figura 11). Estes procedimentos, de processamento posterior e/ou envio para outras máquinas, encontravam-se além

da fronteira do âmbito definido para este trabalho que se limitava à captura das imagens. Como já foi referido, estes serão os passos seguintes deste trabalho, no que se trata a um possível desenvolvimento futuro.

Esta arquitectura serviu de base para o desenvolvimento de todo o trabalho, mas à medida que a sua implementação foi ficando concluída foram acrescentados alguns elementos adicionais que não estavam ainda previstos como a utilização das saídas de vídeo (VGA, HDMI), interfaces de comunicação (USB, Ethernet) da ZedBoard (capítulo 9).

# 7 Implementação

Neste capítulo é apresentada a implementação da arquitectura, apresentada no capítulo anterior, na FPGA ZedBoard.

### 7.1 Vivado Design Suite

Grande parte do trabalho foi desenvolvido usando a Vivado Design Suite<sup>2</sup> da Xilinx de forma a projectar a plataforma de *hardware* que desejávamos carregar na FPGA. Este *software* integra todas as fases do processo de desenvolvimento: para criar podemos optar por escrever o código na própria aplicação, carregar ficheiros já existentes ou em alternativa usar o "IP *Integrator*" que permite criar um diagrama de blocos composto por "IP (*Intellectual Property*) *Cores*", seguindose a possibilidade de simular (como no caso de *test benches*), abrir o diagrama correspondente à análise RTL (*Register Transfer Level*), sintetizar, implementar e por último programar a parte de lógica programável. Todas estas opções podem ser vistas na barra que se situa do lado esquerdo da interface principal do programa denominada "*Flow Navigator*".

A Figura 12 apresenta ainda o sumário de um projecto criado especificamente para a ZedBoard, aparecendo inclusivamente a foto da placa, já que é preciso definir qual o dispositivo em que queremos posteriormente implementar o projecto para que o programa possa lidar com as diferenças existentes ente os diversos dispositivos de forma automática. Depois de completada a fase de síntese e de implementação de um projecto, este sumário também apresenta o relatório das mesmas, indicando possíveis erros assim como as estimativas de consumo energético, utilização de recursos, características temporais (atrasos, caminho crítico, etc.) ou violações das DRC (Design Rule Check(ing)).

<sup>2</sup> Os procedimentos descritos irão estar de acordo com a versão 2015.2 do Vivado, a última disponível à data da escrita deste documento

35

Figura 12 - Interface principal da suite Vivado com destaque para o "Flow Navigator"

## 7.2 Construção do datapath

Definida a arquitetura, avançou-se para a definição do circuito digital. Os módulos começaram a ser incluídos de forma gradual e iam sendo executados testes à medida que iam sendo acrescentados.

Será aqui apresentada uma versão simplificada do caminho de dados em que se procede à captura das imagens provenientes de um módulo de simulação que gera padrões. A base criada para esta situação é então comum a versões posteriores mais elaboradas em que já foi incluída a possibilidade de receber os sinais vindos do painel de instrumentos, e onde também foram acrescentados os módulos de emissão, quer para o ecrã do painel quer para ecrãs externos através das saídas de vídeo da ZedBoard (HDMI, VGA).

De seguida, apresentam-se os diagramas de blocos desta implementação, primeiro na sua versão esquemática (Figura 13), para a enquadrar na arquitetura, e depois na versão criada em "Vivado *Integrator*" (Figura 14).

Figura 13 - Diagrama de blocos (esquemático) da implementação básica

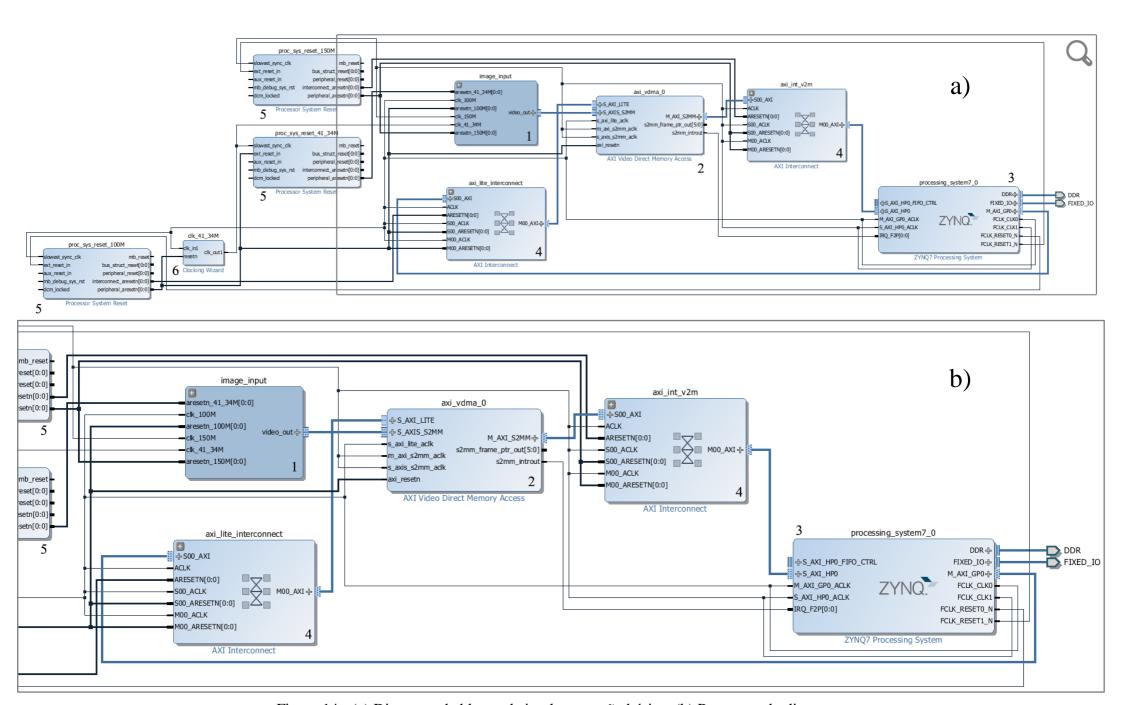

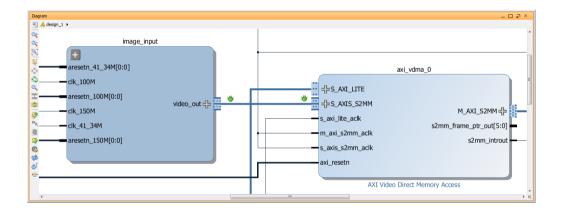

Figura 14 - (a) Diagrama de blocos da implementação básica; (b) Pormenor do diagrama

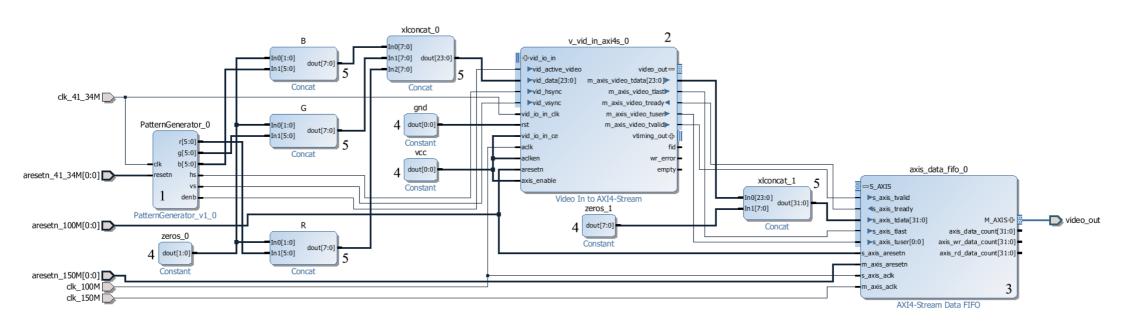

Figura 15 - Composição do bloco "image\_input"

Na Figura 14 é possível visualizar o caminho de dados completo onde se destacam 3 blocos: O bloco composto "image input" que, como pode ser visto na Figura 15, contém o bloco "Video In to AXI4-Stream" e o bloco "AXI4-Stream Data FIFO" permitindo assim a captura das imagens recebidas, neste caso geradas pelo gerador de padrões que pode ser substituído por entradas externas vindas do painel de instrumentos via interface FMC. São ainda usados vários módulos "Concat" e "Constant" de forma a preencher as linhas de dados. Tanto o bloco "Video In to AXI4-Stream" como o bloco "AXI4-Stream Data FIFO" integram FIFOs com a profundidade configurada para 2048 "palavras" para que pudessem armazenar pelo menos uma linha completa da imagem do painel de instrumentos (1280 pixéis de largura). Nó módulo "AXI4-Stream Data FIFO" foi activada a possibilidade de serem usados relógios assíncronos, e assim, a saída já está de acordo com relógio do restante caminho de dados. O bloco "AXI Video Direct Memory Access" gere a transferência dos dados para a memória RAM da placa tratando da conversão dos sinais de uma interface AXI4-Stream para uma AXI4 (Memory-Mapped). Os dados seguem para o bloco seguinte. Foi activada a funcionalidade de sincronizar o módulo usando o sinal "tuser" que tem vindo a ser propagado pelos módulos anteriores ("Video In..." e "...FIFO") e identifica a primeira amostra de cada imagem fazendo com que esta surja alinhada correctamente na memória (primeira amostra de cada *frame* no respectivo endereço de memória), algo que não acontecia nos primeiros testes realizados.

Por último, o bloco "ZYNQ7 Processing System" que representa, como o nome indica, a parte correspondente ao processador (PS) ARM deste SoC Zynq. É essencial a todos os projectos que queiram fazer uso deste processador. Foram activadas duas interfaces AXI: uma HP (<u>High Performance</u>) que recebe os dados vindos do módulo VDMA (<u>Video DMA</u>) e outra GP (<u>General Purpose</u>) para a configuração do mesmo módulo (VDMA). É ainda responsável pela gestão dos sinais de relógio (PLL (<u>Phase-Locked Loop</u>)) e pelos sinais de *reset*.

Os restantes blocos presentes são na maioria gerados automaticamente pelo "IP *Integrator*" e servem essencialmente para sincronizar os sinais de *reset* com os respectivos relógios (blocos "Processor System Reset") intermediar as interfaces AXI (blocos "AXI Interconnect") permitindo que a mesma interface AXI do PS seja usada por vários IP *cores* do restante *datapath*, o que não se verifica neste projecto mas é um procedimento bastante comum (especialmente para ligar várias interfaces AXI4-Lite a um único porto AXI do PS, permitindo assim a configuração, via PS, de diversos IP *cores*). O bloco "Clocking Wizard" permite simular a entrada do sinal de relógio (neste caso foi usado o módulo MMCM (*Mixed-Mode Clock Manager*) para converter o sinal vindo do PS para a frequência desejada).

Depois de concluído o desenho, é necessário criar a *bitstream* com que a FPGA irá ser, posteriormente, programada. Para tal, é usada a opção "*Generate Bitstream*" que pressupõe a prévia execução das fases de síntese e implementação (caso ainda não tenham sido executadas, o programa irá faze-lo de forma automática). Finalizada esta operação, é agora possível exportar a plataforma de *hardware* para o SDK (*Software Development Kit*) da Xilinx e criar o *software* que irá correr no processador ARM (PS).

### 7.2.1 Desenvolvimento de software

Para que uma aplicação faça uso simultâneo da lógica programável (PL) e do *processing* system (PS) no modo standalone, i.e. sem carregar um sistema operativo completo (já que algumas versões do Linux são também suportadas por este processador), são necessárias 3 partes distintas:

- (i) a plataforma de *hardware* exportada do Vivado para o SDK;

- (ii) a aplicação propriamente dita que será desenvolvida no SDK e pode ser escrita em C ou C++;

- (iii) e o chamado <u>Board Support Package</u> (BSP) que introduz uma camada de <u>software</u> intermédia que providencia acesso às funcionalidades básicas do processador como as caches, interrupções e excepções permitindo também interações de entrada e de saída, abortar ou terminar a execução, etc. incluindo ainda os controladores dos módulos criados na lógica programável<sup>3</sup>.

Este BSP é normalmente gerado de forma automática quando se pretende criar uma nova aplicação podendo ser partilhado por diversas aplicações. Pode ainda ser configurado, adicionando bibliotecas de forma a acrescentar funcionalidades sendo possível escolher os controladores e editar os comandos e *flags* de compilação.

Existem alguns *templates* de aplicação ("Hello World", testes de memória e periféricos e alguns *benchmarks*) e é também possível importar alguns exemplos de código para controlar os diferentes periféricos que tenhamos incluído na lógica programável.

\_

<sup>&</sup>lt;sup>3</sup> De acordo com o que é apresentado no SDK quando aberto o ficheiro "system.mss", parte integrante do BSP

### 7.2.2 Notas sobre Interfaces AXI

A grande maioria dos IP *cores* que já se encontravam disponíveis no "IP *Integrator*" do Vivado utiliza interfaces AXI (<u>Advanced eXtensible Interface</u>). [41]

Alguma pesquisa revela que estes protocolos fazem parte da especificação AMBA (<u>Advanced Microcontroller Bus Architecture</u>) que descreve aqueles que são os *standards* "de facto" desta indústria.

Na quarta versão desta especificação (AMBA 4) são definidos os seguintes protocolos que viríamos a utilizar, entre outros [42]:

- AXI4 Para ligações mapeadas em memória (*memory-mapped*), que providenciam uma performance elevada. É fornecido um endereço seguido da transferência de um *burst* de dados até 256 "palavras" (*words*).

- AXI4-Lite Uma versão simplificada da ligação que suporta apenas a transferência de uma "palavra" por ligação. Também é *memory-mapped* o que implica que, neste caso, sejam transferidos um endereço e uma "palavra".

- AXI4-Stream Para um fluxo de dados de alta velocidade, suportando burst's sem restrições de tamanho. Neste protocolo não existe mecanismo de endereçamento e é indicado para um fluxo de dados directo entre a origem e o destino (non memory mapped). [43]

Seria necessário integrar interfaces deste tipo nos módulos criados para que a comunicação com os restantes *cores* fosse possível. Olhando para a breve descrição destes três tipos de interface AXI4 era possível afirmar que uma interface do tipo AXI4-Stream é a mais adequada ao fluxo de vídeo que pretendíamos capturar.

Contudo, não fazia sentido, adaptar desde logo o módulo gerador de padrões para esta interface já que o objectivo deste bloco passava também por simular a forma como os dados iriam entrar, no futuro, na placa e que não se enquadra logo no formato usado neste protocolo. Pareceume mais lógica a possibilidade de dotar a parte de aquisição de dados com este tipo de interface convertendo assim o sinal vindo do painel de instrumentos (ou do simulador) para este padrão e assim poder usar os módulos já existentes no restante *datapath*.

Para tratar desta conversão foi utilizado o IP *core* "Video In to AXI4-Stream" que transforma o conjunto de sinais que compõe o sinal de vídeo (dados, relógio sincronismo), num sinal de acordo com o padrão AXI4-Stream.

### 7.2.3 Módulos criados

Ainda antes da escolha e aquisição da FPGA foram criados alguns módulos genéricos que poderiam vir a ser úteis no seguimento do projecto:

- (i) um módulo que gerasse um padrão para que fosse mais fácil verificar o correcto funcionamento dos restantes elementos do *datapath*;

- (ii) um módulo que recebesse estes dados e os guardasse sendo também responsável por validar esta informação, ignorando os pixéis enviados nos períodos de sincronismo e esperando por o início de uma nova imagem

- (iii) e um módulo que seria responsável pela interface com a memória e que deveria ser do tipo FIFO, como referido anteriormente, por se adequar melhor a este caso. Estes módulos foram desenvolvidos em VHDL (VHSIC (<u>Very High Speed Integrated Circuits</u>) <u>Hardware Description Language</u>) para que pudessem ser implementados independentemente da FPGA que viesse a ser adquirida, uma vez que esta linguagem é, a par da linguagem Verilog, das mais utilizadas para o projecto circuitos digitais e é suportada por praticamente todas as ferramentas de desenvolvimento para equipamentos deste tipo. Acresce-se, a título pessoal, que a linguagem VHDL era, das duas, aquela com que estava mais familiarizado, já que é leccionada e utilizada ao longo do curso (MIEEC).

Destes módulos o único que viria a integrar o *datapath* é o módulo responsável pela gerações de padrões e que pode ser visto na imagem 15 com o nº 1. Todos os restantes módulos incluídos no caminho de dados apresentado fazem parte da biblioteca padrão de IP *cores* do Vivado.

O gerador de padrões irá ser apresentado de seguida enquanto os restantes módulos desenvolvidos, de aquisição e interface com a memória, irão apenas ser apresentados no capítulo 9 destinado ao trabalho complementar, uma vez que não vieram a ser incluídos no *datapath*, tendo sido substituídos pelos módulos "Video In to AXI4-Stream" e "AXI4-Stream Data FIFO" da biblioteca padrão.

#### 7.2.3.1 Gerador de Padrões

Com este módulo pretendíamos criar de padrões para efeitos de teste do restante *datapath*. Em anexo é apresentado o código desenvolvido (Anexo A - 1)) sem interrupções.

```

-- Company: iTGrow

-- Engineer: João Pedro Aleixo Duarte

-- Create Date: 12/15/2014 02:11:13 PM

-- Design Name:

-- Module Name: PatternGenerator - Behavioral

-- Project Name:

-- Target Devices:

-- Tool Versions:

-- Description:

-- Dependencies:

-- Revision:

-- Revision 0.01 - File Created

-- Revision 1.00 - PatternGenerator Created - Detected Sync Error

-- Revision 1.01 - Sync Error Corrected

-- Revision 1.02 - Last Column Error Corrected

-- Additional Comments:

______

library IEEE;

use IEEE.STD LOGIC 1164.all;

use IEEE.NUMERIC STD.all;

library UNISIM;

use UNISIM.VComponents.all;

entity PatternGenerator is

generic (

WIDTH: natural := 1280; --horiztonal display width in pixels

HFRONTPORCH: natural := 2; --horiztonal front porch width in pixels

HSYNCWIDTH : natural := 2; --horiztonal sync pulse width in pixels

HBACKPORCH : natural := 2; --horiztonal back porch width in pixels

HPOL : std logic := '0';

--horizontal sync pulse polarity (1 = positive, 0 = negative)

HEIGHT: natural:= 480; --vertical display width in rows

VFRONTPORCH : natural := 2; --vertical front porch width in rows

VSYNCWIDTH : natural := 2; --vertical sync pulse width in rows

VBACKPORCH : natural := 2; --vertical back porch width in rows

VPOL : std logic := '0';

--vertical sync pulse polarity (1 = positive, 0 = negative)

PTTRN : natural := 0;

RWIDTH : natural := 6;

GWIDTH : natural := 6;

BWIDTH : natural := 6

);

port (

clk : in std logic;

resetn : in std logic; -- Active low

r : out std_logic_vector(RWIDTH - 1 downto 0);

g : out std_logic_vector(GWIDTH - 1 downto 0);

b : out std_logic_vector(BWIDTH - 1 downto 0);

```

```

hs : out std_logic;

vs : out std_logic;

denb : out std_logic

);

end PatternGenerator;

```