Ricardo Jorge Guedes da Silva Nunes da Costa

### AN IEEE1451.0-COMPLIANT FPGA-BASED RECONFIGURABLE WEBLAB

PhD Thesis. Doctoral Program in Information Science and Technology, supervised by Prof. Gustavo Ribeiro da Costa Alves and Prof. Mário Alberto Zenha Rela, submitted to the Faculty of Sciences and Technology of the University of Coimbra

υ 🕠 с ·

#### UNIVERSIDADE DE COIMBRA

Ricardo Jorge Guedes da Silva Nunes da Costa

# An IEEE1451.0-compliant FPGA-based reconfigurable weblab

PhD Thesis Information Sciences and Technologies

Supervisors Gustavo Ribeiro Alves (IPP/ISEP/DEE) Mário Zenha Rela (FCTUC/DEI)

Department of Informatics Engineering Faculty of Science and Technology University of Coimbra

January/2014

UNIVERSIDADE DE COIMBRA

## Abstract

Technology evolution is contributing for a sustainable change in engineering education. New resources and tools are continuously improving the teaching and learning processes, providing more pathways to both students and teachers for accessing better educational contents. In engineering courses, the experimental work, typically supported by traditional laboratories, is also encompassing technology evolution as denoted by the appearance of the so-called weblabs or remote laboratories. This type of laboratories allows both students and teachers to remotely access physical experiments enabling the control of laboratory equipment through a simple device connected to the Internet (e.g. a PC). Besides the provided flexibility (e.g. access to a real laboratory on a 24x7 basis) other advantages may be enumerated, such as the increase on students' motivation and the cost reductions for all the involved actors in the teaching and learning process (e.g. students, teachers, institutions, etc.). However, current weblabs' architectures and their underlying infrastructures follow specific and distinct technical implementations, i.e. there is no standard solution. Moreover, they are not able to be reconfigured with different instruments and modules, known as weblab modules. Whenever required in a traditional laboratory, these modules can be attached to the target experiments, provided that they are available in the laboratory facilities. Some weblabs' implementations allow setting up connections between the target experiments and the weblab modules provided in the infrastructure, but these modules cannot be changed or replicated, i.e. the flexibility for changing the layout and the modules used in a particular weblab infrastructure is very reduced. Therefore, the lack of a standard access and design of weblabs, and the reduced flexibility for changing the required modules for conducting the target experiments, are two issues that are preventing their wide-spread adoption in engineering education.

This thesis describes a research work conducted to design standardbased reconfigurable weblabs. It analyses the possibility of using the IEEE1451.0 Std. to design the weblabs and the modules adopted by the underlying infrastructures to control/monitor the target experiments. Additionally, to provide reconfiguration capability to the weblab infrastructure, it considers the use of Field Programmable Gate Arrays (FPGAs) for accommodating the weblab modules, thus allowing: i) the use of standard Hardware Description Languages (HDLs) to describe the weblab modules, making them easily sharable and replicable and; ii) the weblab infrastructures to inherit the reconfigurable nature of FPGAs, making them flexible in order to accommodate different embedded modules with the inherent reduction of costs that may arise from replacing traditional with embedded instrumentation.

Besides contextualizing the role of weblabs in engineering education, presenting some examples and commenting the use of traditional instrumentation standards for their design, the thesis describes the IEEE1451.0 Std., suggesting extensions for its adoption in the design of weblabs. Supported on those suggestions and on FPGA technologies, it specifies the development of an IEEE1451.0-compliant reconfigurable weblab prototype and presents and analyses researchers' opinions about its use and the benefits for engineering education.

### **Keywords**

Remote experimentation, Weblabs, Remote laboratories, IEEE1451.0 Std., FPGAs, Hardware reconfiguration.

## Resumo

A evolução da tecnologia tem contribuído para uma mudança sustentada na educação em engenharia. Novos recursos e ferramentas têm melhorado os processos de ensino e aprendizagem facilitando a alunos e professores o acesso a melhores conteúdos educativos. No caso particular dos cursos de engenharia, o trabalho experimental, tipicamente realizado em laboratórios tradicionais, tem sofrido alterações com base na evolução tecnológica, de que é exemplo o aparecimento dos denominados laboratórios remotos. Este tipo de laboratórios permite que alunos e professores possam aceder a experiências reais controlando remotamente o equipamento laboratorial através de um simples dispositivo ligado à Internet (e.g. PC). Para além da flexibilidade fornecida (acesso a um laboratório real 24 horas por dia, 7 dias por semana) outras vantagens podem ser enumeradas, tais como a crescente motivação dos alunos para a realização de trabalhos experimentais e a inerente redução de custos que estes laboratórios podem trazer para todos os actores envolvidos no processo de ensino e aprendizagem (alunos, professores, instituições, etc.). Contudo, as atuais arquiteturas de laboratórios remotos, bem como as infraestruturas subjacentes, seguem implementações técnicas distintas e específicas, i.e. não existe uma solução normalizada que suporte a reconfiguração com diferentes instrumentos e módulos, ambos genericamente denominados por módulos de laboratório. Quando necessário, esses módulos podem ser interligados às experiências em teste, desde que disponíveis nas instalações onde se encontra o laboratório. Algumas implementações de laboratórios remotos permitem a interligação das experiências com os módulos de laboratório disponíveis na infraestrutura subjacente. Contudo, esses módulos não podem ser substituídos ou replicados, i.e. a flexibilidade para modificar o *layout* e os módulos utilizados numa dada infraestrutura é ainda reduzida. Neste contexto, a inexistência de um acesso e desenvolvimento normalizados para laboratórios remotos, e a reduzida flexibilidade para substituir/replicar os módulos necessários para a realização de uma dada experiência, são dois aspetos que têm dificultado a disseminação e a utilização deste tipo de laboratórios na educação em engenharia.

Esta tese descreve o trabalho de investigação realizado com vista ao desenvolvimento de laboratórios remotos normalizados e reconfiguráveis. Analisa-se a possibilidade de utilizar a norma IEEE1451.0 para o desenvolvimento de laboratórios remotos e de módulos usados pela infraestrutura subjacente para controlar/monitorar

as experiências. Adicionalmente, para fornecer capacidade de reconfiguração à infraestrutura laboratorial, sugere-se a utilização de dispositivos lógicos reconfiguráveis (Field Programmable Gate Arrays, FPGAs) para suportar os módulos de laboratório, permitindo desta forma: i) a utilização de linguagens normalizadas de descrição de hardware (Hardware **Description** Languages, HDLs) para а especificação dos módulos do laboratório, tornando-os facilmente partilháveis e replicáveis e; ii) que a infraestrutura herde a capacidade de reconfiguração das FPGAs, tornando-a flexível para suportar diferentes módulos de laboratório com a inerente redução de custos que uma solução semelhante pode trazer quando se substitui instrumentação tradicional por embutida.

Para além de contextualizar o papel dos laboratórios remotos na educação em engenharia, da apresentação de alguns exemplos e comentários sobre a utilização de normas de instrumentação para a sua especificação, a tese descreve a norma IEEE1451.0. Sugerem-se extensões a esta norma para a sua adoção na especificação e implementação de laboratórios remotos. Tendo por base essas sugestões e a utilização de FPGAs, esta tese especifica o desenvolvimento de um laboratório remoto reconfigurável e compatível com a norma IEEE1451.0, e apresenta opiniões de investigadores sobre a sua utilização e benefício para a educação em engenharia.

#### **Palavras chave**

Experimentação remota, Laboratórios remotos, norma IEEE1451.0, FPGAs, Reconfiguração de hardware.

## Acknowledgments

Completing a PhD is a truly marathon that represents a conclusion stage of several years of dedication and enthusiasm that I would not have been able to complete without the contribution of several people and institutions.

I must first express my gratitude to my advisors; Professors Mário Rela from UC/FCTUC and Gustavo Alves from IPP/ISEP. Their leadership, support and attention were fundamental to achieve the proposed objectives of my work. It must be emphasized the important contribution of Professor Gustavo Alves, since he gave me a constant incentive to conclude the different phases of the work, and the guidance to face the difficulties encountered during this long journey. Without disregarding other contributions, I must truly express my gratitude to his availability for helping me and advising me.

Over these years I have enjoyed the aid of several fellows that I would like to thanks. In particular to the people of the LABORIS research group, that was my host place during the PhD, in particular to André Fidalgo, Carlos Felgueiras, Manuel Gericota and Paulo Ferreira, and to my PhD colleagues that someway helped me during my visits to Coimbra.

At this moment I could not forget the reasons that led me to attend this PhD, in particular my previous involvement in the area of remote laboratories during my participation in an European project at FEUP. In this institution, I had some people that also contributed to achieve this final result, that I would like to express my gratitude, in particular to António Cardoso, Inês Cambeiro, Telmo Amaral, Miguel Silva and to Professor José Martins Ferreira.

Despite all the difficulties faced during the PhD, most of them related with the economical restrictions imposed to science in Portugal, the help of IPP/ISEP was fundamental. Through a PROTEC program promoted by the Portuguese government, and latter by an IPP/ISEP autonomous support, some of the expenses with academic fees, travels and papers publications, were financed. Moreover, it was possible to reduce the number of teaching hours at the DEE/ISEP during the first years, which gave me more time for the PhD research activities and to conclude the courses of the first year.

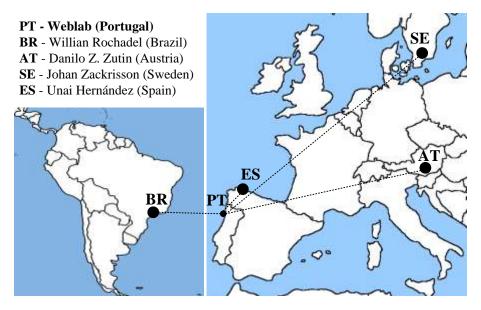

During the validation & verification process, some researchers had a fundamental contribution. I would like to express my thanks to them, namely to Unai Hernández, Danilo Zutin, Willian Rochadel and Johan Zackrisson.

Last but not least; I would like to express my gratitude to my family and friends for their important support, which gave me the required emotional stability to conclude this important phase of my academic life.

## Notes to the reader

While writing an extensive document, it is usual to take decisions that aim to facilitate the reading and understanding of its contents.

Therefore, it was decided to create a list of acronyms and abbreviations, and a glossary with the most relevant terms and expressions found in the text. All acronyms, and most of the abbreviations, are presented in capital letters. They are typically specified only once, but the most relevant ones can be specified in more than one chapter or annex. The most common in science (e.g. CD) and the majority of those specifying names of conferences and institutions, are only defined in the acronyms and abbreviations list.

To emphasize some terms and expressions during the thesis, the *italic* style was applied. Terms written in a different font from the remaining text refer to commands or software code.

It was also decided to put some of the information and technical descriptions into annex. The criterion for the decisions was supported by their relevance, without hinder the access to specific details readers may want to consult, such as implementation details that are provided in some annexes.

Most of the references to webpages describing software applications, tools, and specific technical information, were placed in footnotes, rather then listing them in the reference's section.

The DVD attached to this thesis provides some of the material referred during the text, namely:

- an introductory webpage with the list of published papers;

- software packages;

- the supporting webpage used during the validation & verification process described in chapter 7;

- videos exemplifying the validation & verification process;

- photographs of the developed weblab;

- this same thesis in a Portable Document Format (PDF).

## Contents

| СНАРТЕН                                                                       | R1 INTRODUCTION                                                                                                                                                                                                                                                                                    | .1                                                          |

|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|                                                                               | CKGROUND AND MOTIVATION                                                                                                                                                                                                                                                                            |                                                             |

|                                                                               | OVATIVE ASPECTS<br>UCTURE AND ORGANIZATION                                                                                                                                                                                                                                                         |                                                             |

|                                                                               |                                                                                                                                                                                                                                                                                                    |                                                             |

|                                                                               | <b>R 2</b> WEBLABS IN ENGINEERING EDUCATION                                                                                                                                                                                                                                                        |                                                             |

|                                                                               | ROLE OF EXPERIMENTAL WORK IN ENGINEERING EDUCATION<br>ORATORY TYPES FOR CONDUCTING EXPERIMENTAL WORK                                                                                                                                                                                               |                                                             |

|                                                                               | VTEXTUAL ANALYSIS OF WEBLABS                                                                                                                                                                                                                                                                       |                                                             |

| 2.3.1                                                                         | Fundamentals of the Actor-Network Theory                                                                                                                                                                                                                                                           | .18                                                         |

|                                                                               | Influencing contexts                                                                                                                                                                                                                                                                               |                                                             |

|                                                                               | Involved actors and associations                                                                                                                                                                                                                                                                   |                                                             |

|                                                                               | AGOGICAL AND TECHNICAL CONSIDERATIONS ON WEBLABS                                                                                                                                                                                                                                                   |                                                             |

|                                                                               | Meeting experimental learning goals with weblabs<br>Mapping pedagogical goals against weblabs' capabilities                                                                                                                                                                                        |                                                             |

|                                                                               | Traditional weblab architecture                                                                                                                                                                                                                                                                    |                                                             |

|                                                                               | Involved technologies for implementing weblabs                                                                                                                                                                                                                                                     |                                                             |

|                                                                               | BLAB ARCHITECTURES: A BRIEF OVERVIEW                                                                                                                                                                                                                                                               |                                                             |

|                                                                               | MIT iLab project                                                                                                                                                                                                                                                                                   |                                                             |

|                                                                               | NetLab                                                                                                                                                                                                                                                                                             |                                                             |

|                                                                               | Other weblabs and projects                                                                                                                                                                                                                                                                         |                                                             |

|                                                                               | RRENT LIMITATIONS AND PROBLEMS OF WEBLABS                                                                                                                                                                                                                                                          |                                                             |

| 2.7. Sum                                                                      | 1MARY                                                                                                                                                                                                                                                                                              | .41                                                         |

| СНАРТЕН                                                                       | <b>R 3</b> CONSIDERATIONS FOR DESIGNING STANDARD AND                                                                                                                                                                                                                                               |                                                             |

|                                                                               | RECONFIGURABLE WEBLABS                                                                                                                                                                                                                                                                             | .43                                                         |

|                                                                               | BLAB ARCHITECTURES BASED ON INSTRUMENTATION STANDARDS                                                                                                                                                                                                                                              |                                                             |

|                                                                               | Stand-alone and modular instrumentation                                                                                                                                                                                                                                                            |                                                             |

|                                                                               | Instrumentation standards<br>Hybrid architectures                                                                                                                                                                                                                                                  |                                                             |

|                                                                               | Embedded instrumentation.                                                                                                                                                                                                                                                                          |                                                             |

|                                                                               | GOING INITIATIVES FOR WEBLABS STANDARDIZATION: GOLC AND IEEEp1876 Std                                                                                                                                                                                                                              |                                                             |

|                                                                               | NG AND EXTENDING THE IEEE1451.0 STD. FOR DESIGNING WEBLABS                                                                                                                                                                                                                                         |                                                             |

|                                                                               | Overview of the IEEE1451.0 Std.                                                                                                                                                                                                                                                                    |                                                             |

|                                                                               | Overview of current projects and research<br>Adopting the IEEE1451.0 Std. for weblabs                                                                                                                                                                                                              |                                                             |

|                                                                               | VIDING RECONFIGURABILITY TO WEBLABS THROUGH FPGAS                                                                                                                                                                                                                                                  |                                                             |

|                                                                               | Infrastructure                                                                                                                                                                                                                                                                                     |                                                             |

|                                                                               | Remote access                                                                                                                                                                                                                                                                                      |                                                             |

| 3.5. Sum                                                                      |                                                                                                                                                                                                                                                                                                    |                                                             |

| СНАРТЕК                                                                       | 1MARY                                                                                                                                                                                                                                                                                              | .70                                                         |

|                                                                               | IMARY<br>R 4 THE IEEE1451.0 STD. AS A SMART FRAMEWORK FOR WEBLABS.                                                                                                                                                                                                                                 |                                                             |

| 4.1. Ref                                                                      | <b>R 4 THE IEEE1451.0 STD. AS A SMART FRAMEWORK FOR WEBLABS.</b><br>ERENCE MODEL: NCAP AND TIM SMART MODULES                                                                                                                                                                                       | <b>.73</b><br>.75                                           |

| 4.1. Ref<br>4.2. Tra                                                          | <b>R 4 THE IEEE1451.0 STD. AS A SMART FRAMEWORK FOR WEBLABS.</b><br>erence model: NCAP and TIM smart modules<br>insducer Electronic Data Sheets                                                                                                                                                    | <b>.73</b><br>.75<br>.76                                    |

| 4.1. Ref<br>4.2. Tra<br>4.3. Sma                                              | <b>R 4 THE IEEE1451.0 STD. AS A SMART FRAMEWORK FOR WEBLABS.</b><br>ERENCE MODEL: NCAP AND TIM SMART MODULES<br>INSDUCER ELECTRONIC DATA SHEETS                                                                                                                                                    | <b>.73</b><br>.75<br>.76<br>.80                             |

| 4.1. REF<br>4.2. TRA<br>4.3. SMA<br>4.3.1                                     | <b>R 4 THE IEEE1451.0 STD. AS A SMART FRAMEWORK FOR WEBLABS.</b><br>ERENCE MODEL: NCAP AND TIM SMART MODULES<br>INSDUCER ELECTRONIC DATA SHEETS                                                                                                                                                    | <b>.73</b><br>.75<br>.76<br>.80<br>.81                      |

| 4.1. REF<br>4.2. TRA<br>4.3. SMA<br>4.3.1<br>4.3.2<br>4.3.3                   | <b>R 4 THE IEEE1451.0 STD. AS A SMART FRAMEWORK FOR WEBLABS.</b><br>ERENCE MODEL: NCAP AND TIM SMART MODULES.<br>INSDUCER ELECTRONIC DATA SHEETS.<br>ART MODULES: ACCESS AND OPERATION.<br>Addressing mechanism.<br>Operating states and modes.<br>Status registers and the status-event protocol. | .73<br>.75<br>.76<br>.80<br>.81<br>.82<br>.84               |

| 4.1. REF<br>4.2. TRA<br>4.3. SMA<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4          | R 4 THE IEEE1451.0 STD. AS A SMART FRAMEWORK FOR WEBLABS.<br>ERENCE MODEL: NCAP AND TIM SMART MODULES.<br>INSDUCER ELECTRONIC DATA SHEETS.<br>ART MODULES: ACCESS AND OPERATION.<br>Addressing mechanism.<br>Operating states and modes                                                            | .73<br>.75<br>.76<br>.80<br>.81<br>.82<br>.84<br>.85        |

| 4.1. REF<br>4.2. TRA<br>4.3. SMA<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5 | <b>R 4 THE IEEE1451.0 STD. AS A SMART FRAMEWORK FOR WEBLABS.</b><br>ERENCE MODEL: NCAP AND TIM SMART MODULES.<br>INSDUCER ELECTRONIC DATA SHEETS.<br>ART MODULES: ACCESS AND OPERATION.<br>Addressing mechanism.<br>Operating states and modes.<br>Status registers and the status-event protocol. | .73<br>.75<br>.76<br>.80<br>.81<br>.82<br>.84<br>.85<br>.86 |

| 4.5. SUGGESTED WEBLAB INFRASTRUCTURES COMPLIANT WITH THE IEEE1451.0 STD<br>4.6. Extending the IEEE1451.0 Std. to enhance weblab architectures |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.6.1 Suggested architecture                                                                                                                  |     |

| 4.6.1 Suggested arcmeeture                                                                                                                    |     |

| 4.6.3 Operational sequence                                                                                                                    |     |

| 4.7. A THIN IMPLEMENTATION OF THE IEEE1451.0 STD. APPLIED TO WEBLABS                                                                          | 101 |

| CHAPTER 5 A WEBLAB IMPLEMENTATION SUPPORTED BY FPGA-BASED                                                                                     | 105 |

| BOARDS                                                                                                                                        | 105 |

| 5.1. OVERALL ARCHITECTURE: WEBLAB SERVER AND UNDERLYING INFRASTRUCTURE                                                                        |     |

| 5.2. THE WEBLAB INFRASTRUCTURE: NCAP AND FPGA-BASED TIM                                                                                       |     |

| 5.2.1 The NCAP-TIM interface                                                                                                                  |     |

| 5.2.2 The NCAI                                                                                                                                |     |

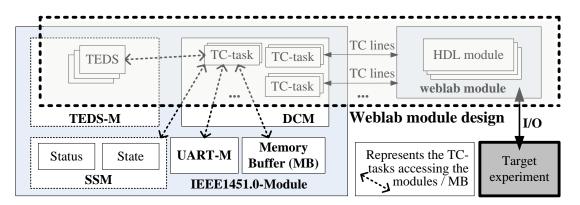

| 5.3. AN IEEE1451.0-COMPLIANT MODULE FOR BINDING WEBLAB MODULES                                                                                |     |

| 5.4. WEBLAB ACCESSING MECHANISMS                                                                                                              | 115 |

| 5.5. THE WEBLAB RECONFIGURATION TOOL                                                                                                          |     |

| 5.6. SUMMARY                                                                                                                                  | 121 |

| CHAPTER 6 THE WEBLAB RECONFIGURABLE FRAMEWORK                                                                                                 |     |

| 6.1. INVOLVED RESOURCES AND TOOLS                                                                                                             |     |

| 6.2. STRUCTURE AND FUNCTIONALITY OF THE IEEE1451.0-COMPLIANT MODULE                                                                           |     |

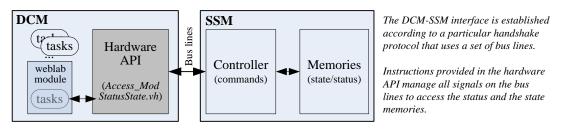

| 6.2.1 Decoder/Controller Module (DCM)                                                                                                         |     |

| <ul><li>6.2.2 TEDS-Module (TEDS-M)</li><li>6.2.3 Status/State Module (SSM)</li></ul>                                                          |     |

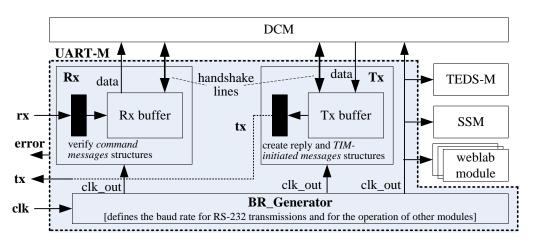

| 6.2.4 UART Module (UART-M)                                                                                                                    |     |

| 6.3. THE WEBLAB CONNECTING MODULES: LAYOUT AND INTERFACE                                                                                      | 139 |

| 6.3.1 Internal architecture                                                                                                                   | 139 |

| 6.3.2 Required Transducer Channels                                                                                                            |     |

| 6.3.3 TC-tasks                                                                                                                                |     |

| 6.3.4 Development methodology                                                                                                                 |     |

| 6.4. THE RECONFIGURATION PROCESS                                                                                                              |     |

| <ul><li>6.4.1 The reconfiguration sequence</li><li>6.4.2 The role of the configuration file</li></ul>                                         |     |

| 6.4.3 Implementation issues of the RecTool                                                                                                    |     |

| 6.5. SUMMARY                                                                                                                                  |     |

| CHAPTER 7 VALIDATION & VERIFICATION                                                                                                           | 157 |

| 7.1. Adopted strategy: scenario and objectives                                                                                                | 159 |

| 7.2. ACTORS INVOLVED: RESEARCHERS, EXPERIMENTS AND TOOLS                                                                                      |     |

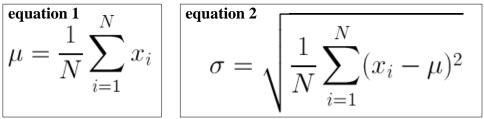

| 7.3. Applied methodology                                                                                                                      |     |

| 7.4. REPORTED RESULTS AND CORRESPONDING ANALYSIS                                                                                              |     |

| <ul><li>7.4.1 Current weblabs' problems</li><li>7.4.2 Operation of the implemented weblab</li></ul>                                           | 169 |

| 7.4.2 Operation of the implemented weblab                                                                                                     |     |

| 7.5. SUMMARY                                                                                                                                  |     |

| CHAPTER 8 CONCLUSIONS AND FUTURE WORK                                                                                                         |     |

| 8.1. Adopted architecture: IMPLICATIONS FOR THE EXPERIMENTAL WORK IN ENGINEERING                                                              |     |

| EDUCATION                                                                                                                                     |     |

| 8.2. FUTURE WORK PERSPECTIVES                                                                                                                 |     |

| 8.3. CONCLUDING REMARKS                                                                                                                       | 187 |

| REFERENCES                                                                                                                                    | 189 |

| ANNEXES                                                                                                                                       | 203 |

| ANNEX A FPGA INTERNAL ARCHITECTURE OVERVIEW                                                                                                   | 205 |

| ANNEX B EXAMPLE OF AN FPGA-BASED BOARD                                                                                        | 207 |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| ANNEX C FPGA RECONFIGURATION: OPTIONS FOR WEBLABS                                                                             | 209 |

| ANNEX D TEDS: EXAMPLES, ATTRIBUTES AND STATUS                                                                                 | 211 |

| ANNEX E SENSORS AND ACTUATORS TRIGGER STATES                                                                                  | 215 |

| ANNEX F IEEE1451.0 STATUS BITS                                                                                                | 217 |

| ANNEX G NEW IEEE1451.0 HTTP API METHODS AND INTERFACES                                                                        | 219 |

| ANNEX H MAPPING IEEE1451.0 HTTP API METHODS AND COMMANDS                                                                      | 225 |

| ANNEX I ERROR CODES RETRIEVED FROM THE NCAP                                                                                   | 231 |

| ANNEX J THE IEEE1451.0-COMPLIANT MODULE                                                                                       | 233 |

| J.1 - DCM INTERNAL REGISTERS                                                                                                  | 233 |

| J.2 - DCM INTERNAL AND COMMAND TASKS                                                                                          | 235 |

| J.2.1 - Internal tasks                                                                                                        |     |

| J.2.2 - Command-tasks                                                                                                         |     |

| J.3 - DCM SCHEMATICS                                                                                                          |     |

| J.4 - THE DCM-MB INTERFACE<br>J.5 - THE DCM-MT INTERFACE                                                                      |     |

| J.5 - THE DCM-MT INTERFACE<br>J.6 - DCM REGISTERS AND BUSES FOR IMPLEMENTING THE ERROR DETECTION MECHANISM                    |     |

| J.7 - ERROR CODES SPECIFIED IN THE IEEE1451.0-MODULE                                                                          |     |

| J.8 - TEDS-M: SCHEMATICS AND INTERFACE                                                                                        |     |

| J.8.1 - Internal variables                                                                                                    |     |

| J.8.2 - Schematics and signals                                                                                                |     |

| J.8.3 - Handshake protocol                                                                                                    |     |

| J.8.4 - Hardware API                                                                                                          |     |

| J.9 - SSM: SCHEMATICS AND INTERFACE                                                                                           |     |

| J.9.1 - Internal variables                                                                                                    |     |

| J.9.2 - Schematics and signals<br>J.9.3 - Handshake protocol                                                                  |     |

| J.9.5 - Handshake protocol<br>J.9.4 - Hardware API                                                                            |     |

| J.10 - UART-M: SCHEMATICS AND INTERFACE                                                                                       |     |

| J.10.1 - Schematics and signals                                                                                               |     |

| J.10.1 - Schematics and signals                                                                                               |     |

| -                                                                                                                             |     |

| ANNEX K WEBLAB MODULES: SPECIFICATION AND DESIGN                                                                              |     |

| K.1 - DEFINITION OF TC-TASKS                                                                                                  |     |

| K.2 - DESIGN OF TEDSS AND MTS<br>K.3 - Examples of weblab modules                                                             |     |

| K.3.1 - Digital I/O modules                                                                                                   |     |

| K.3.2 - Step-Motor Controller Module (SMCM)                                                                                   |     |

| K.3.3 - Event sensor                                                                                                          |     |

| ANNEX L RECONFIGURATION                                                                                                       | 267 |

| L.1 - Examples of report files created during the reconfiguration process                                                     |     |

| L.1 - EXAMPLES OF REPORT FILES CREATED DURING THE RECONFIGURATION PROCESS<br>L.2 - EXAMPLE OF A CONFIGURATION FILE            |     |

| L.3 - THE RECONFIGURATION SCHEMATICS                                                                                          |     |

| L.4 - SOME EXAMPLES OF HDL FILES CREATED BY THE RECONFIGURATION PROCESS                                                       | 274 |

| L.5 - EXAMPLES OF FPGA RESOURCES UTILIZATION                                                                                  |     |

| L.6 - EXAMPLE OF TCL FILE CREATED DURING RECONFIGURATION                                                                      |     |

| ANNEX M VALIDATION & VERIFICATION                                                                                             |     |

| M.1 - SUPPORTING WEBPAGE: THE MAIN PAGE                                                                                       |     |

| M.2 - SCREENSHOTS OF VIDEOS EXEMPLIFYING THE INTERACTION WITH THE WEBLAB<br>M.3 - QUESTIONNAIRES PROVIDED FOR THE RESEARCHERS |     |

| M.5 - QUESTIONNAIRES PROVIDED FOR THE RESEARCHERS                                                                             |     |

|                                                                                                                               |     |

# Figures

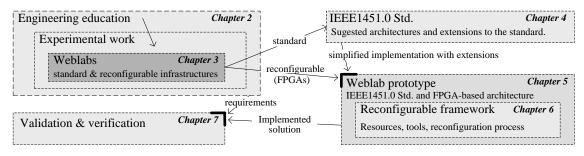

| Figure 1.1: Conceptual diagram with the thesis structure.                                | 6  |

|------------------------------------------------------------------------------------------|----|

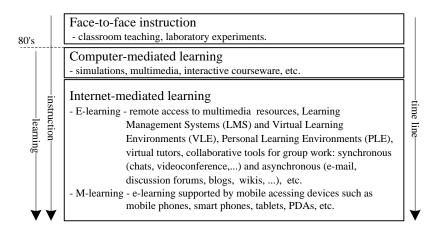

| Figure 2.1: Educational landscape since the 80's.                                        | 11 |

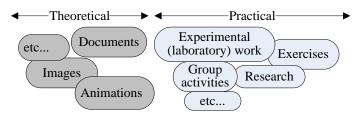

| Figure 2.2: Theoretical and practical components of an engineering course                | 13 |

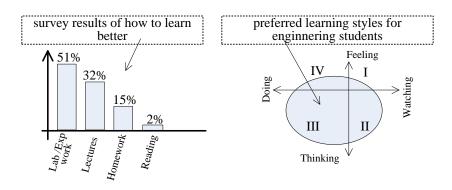

| Figure 2.3: Preferred learning styles in engineering courses                             | 13 |

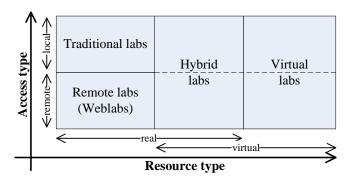

| Figure 2.4: Laboratory types available for conducting experimental activities.           | 15 |

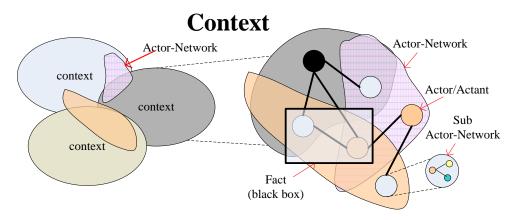

| Figure 2.5: Conceptual model of the Actor-Network Theory                                 | 19 |

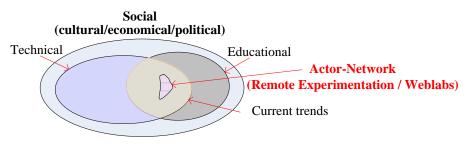

| Figure 2.6: Situating RE as an actor-network                                             | 20 |

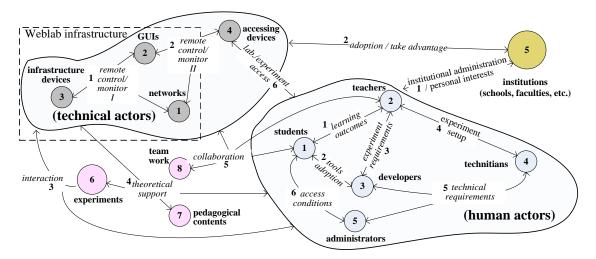

| Figure 2.7: Weblabs in the RE actor-network.                                             | 21 |

| Figure 2.8: Pedagogical/technical issues for adopting weblabs in engineering education   | 27 |

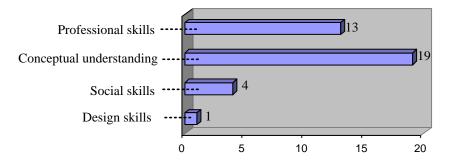

| Figure 2.9: Division of a set of papers according to discussed weblabs pedagogical goals |    |

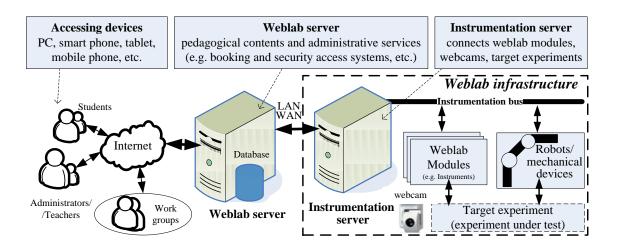

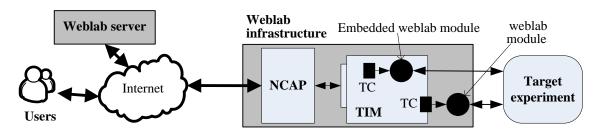

| Figure 2.10: A coarse model of a typical weblab architecture                             | 31 |

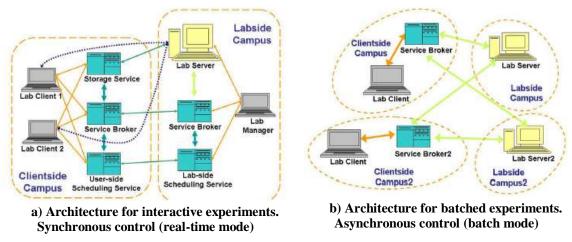

| Figure 2.11: Topologies of the iLab Shared Architecture (ISA).                           | 35 |

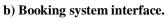

| Figure 2.12: NetLab architecture overview                                                |    |

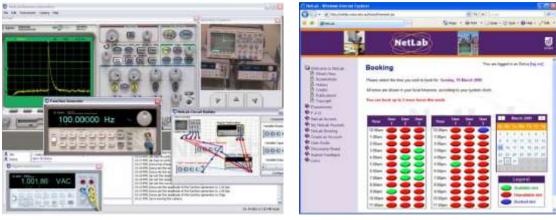

| Figure 2.13: NetLab web interfaces                                                       | 37 |

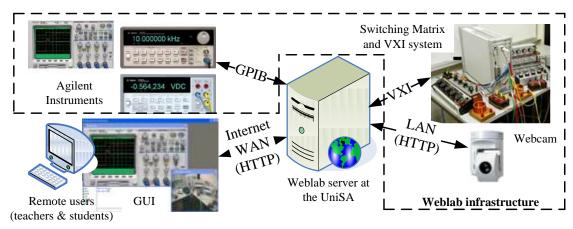

| Figure 2.14: Overview of a VISIR architecture based on the PXI bus.                      |    |

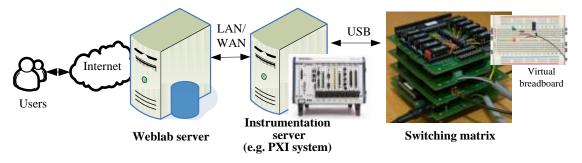

| Figure 2.15: Interfaces used in the VISIR project.                                       |    |

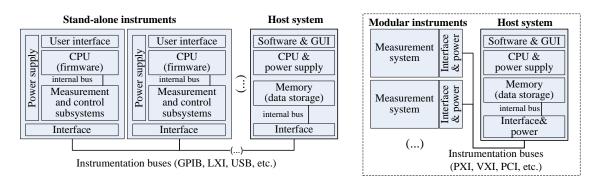

| Figure 3.1: Stand-alone and modular instrumentation                                      | 45 |

| Figure 3.2: A layered architecture for an instrumentation system.                        | 46 |

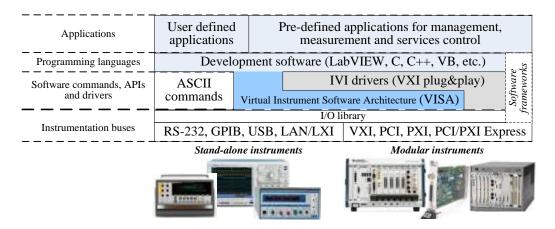

| Figure 3.3: Example of an hybrid system applicable to weblab infrastructures             | 50 |

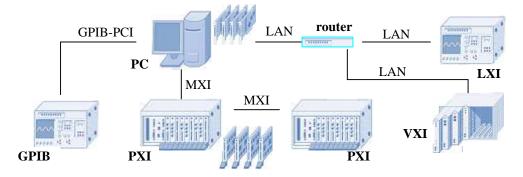

| Figure 3.4: Architectures for embedded instruments in weblab infrastructures             | 52 |

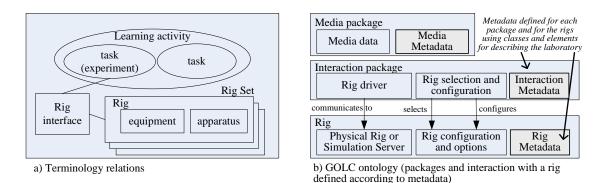

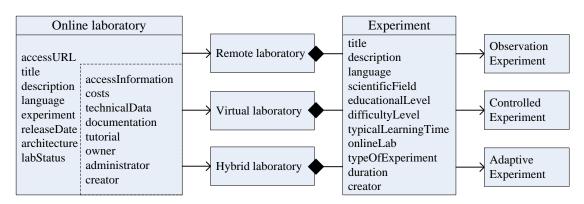

| Figure 3.5: Overview of the Global Online Laboratory Consortium.                         | 54 |

| Figure 3.6: Current terminology and ontology defined by the GOLC.                        | 55 |

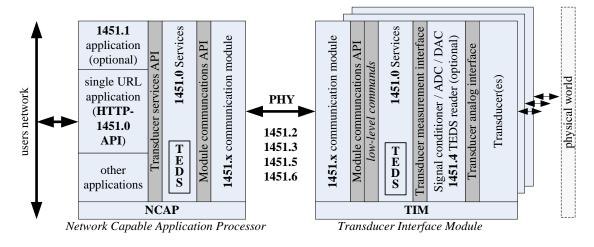

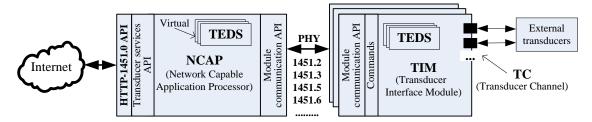

| Figure 3.7: Reference model of the IEEE1451.0 Std                                        | 57 |

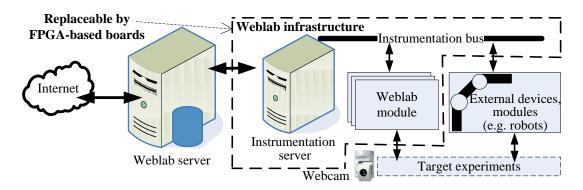

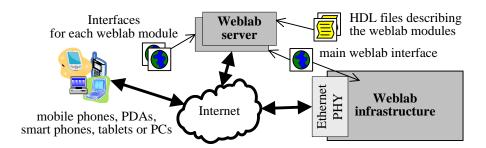

| Figure 3.8: FPGA-based reconfigurable weblab infrastructure.                             | 64 |

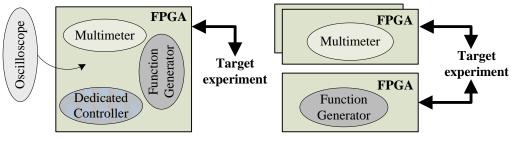

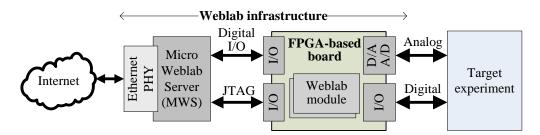

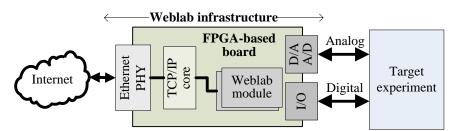

| Figure 3.9: Architectures for embedding weblab modules in FPGA-based boards.             | 64 |

| Figure 3.10: Proposed weblab architecture using FPGA-based weblabs.                      | 65 |

| Figure 3.11: Hybrid solution for remote accessing weblab infrastructures.                | 66 |

| Figure 3.12: SoC solution for remote accessing weblab infrastructures.                   | 67 |

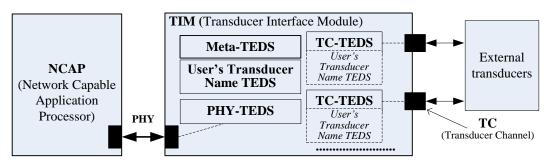

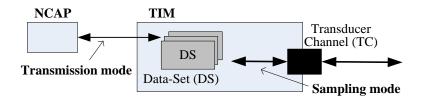

| Figure 4.1: Reference model of the IEEE1451.0 Std                                        | 75 |

| Figure 4.2: Mandatory TEDSs in an IEEE1451.0 compatible device                           | 77 |

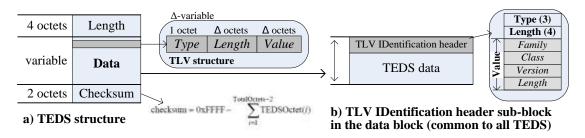

| Figure 4.3: Diagram illustrating the group of TEDSs defined in the IEEE1451.0 Std        | 79 |

| Figure 4.4: Structure and identification header defined for all TEDSs.                   | 79 |

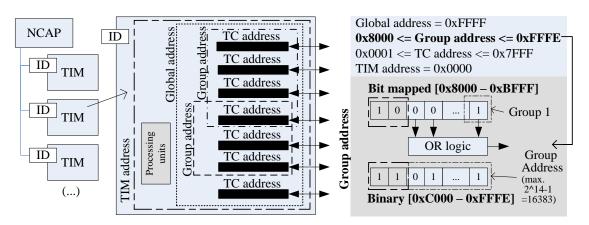

| Figure 4.5: Addressing mechanism used by the IEEE1451.0 Std                              |    |

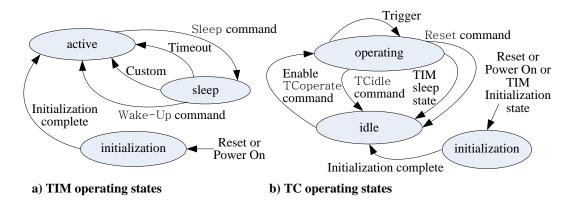

| Figure 4.6: TIM and TC operating states.                                                                                           | 82  |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.7: Conceptual diagram of the TIM operation modes                                                                          | 83  |

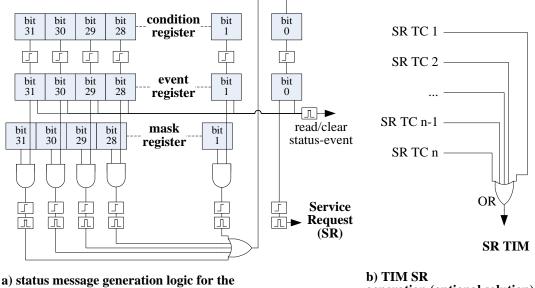

| Figure 4.8: Status message generation logic and TIM SR generation                                                                  | 85  |

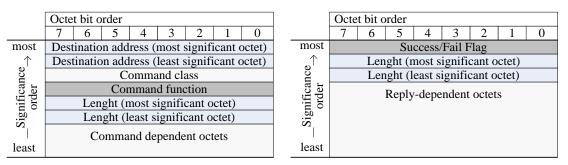

| Figure 4.9: Message structures                                                                                                     | 85  |

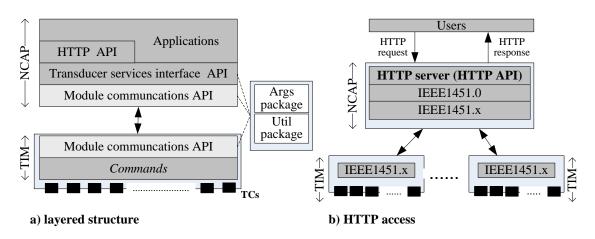

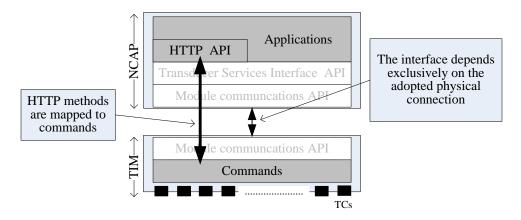

| Figure 4.10: IEEE1451.0 Std. API layered structure and the HTTP schematic access.                                                  | 88  |

| Figure 4.11: Adopting the IEEE1451.0 Std. for designing a weblab infrastructure                                                    | 90  |

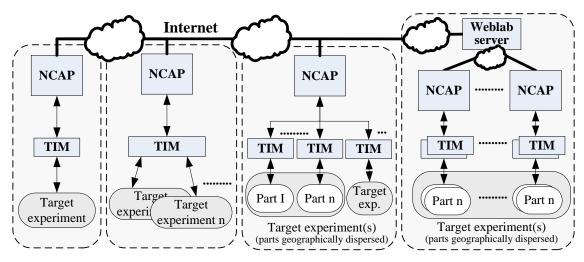

| Figure 4.12: Possible weblab infrastructures based on the IEEE1451.0 Std                                                           | 91  |

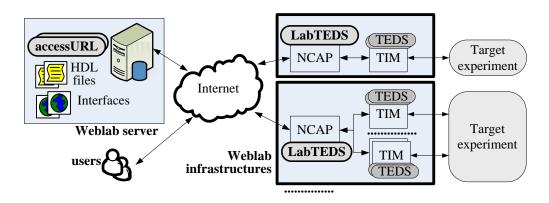

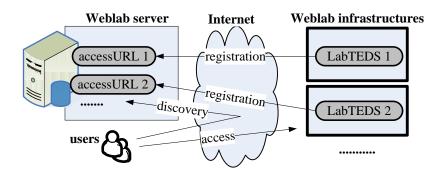

| Figure 4.13: Suggested weblab architecture based on the IEEE1451.0 Std                                                             | 94  |

| Figure 4.14: Lab2go Metadata - Reference Model Specification.                                                                      | 95  |

| Figure 4.15: Operational sequence for accessing weblab infrastructures                                                             | 97  |

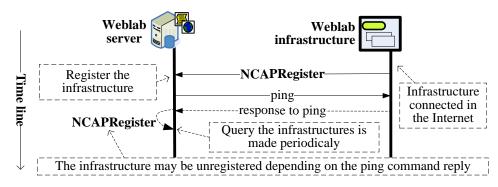

| Figure 4.16: Process for registering/unregistering weblab infrastructures                                                          | 98  |

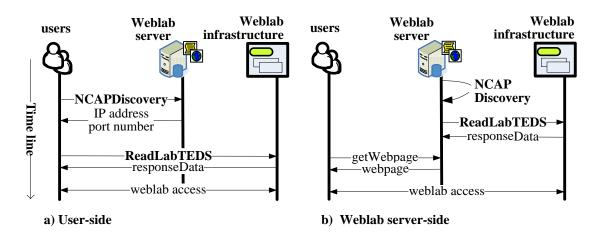

| Figure 4.17: Using the NCAPDiscovery and ReadLabTEDS methods to access registered weblab infrastructures.                          | 99  |

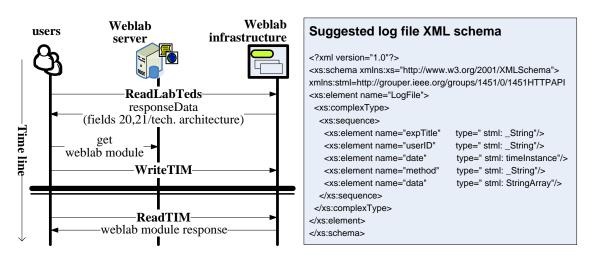

| Figure 4.18: Using the WriteTIM and ReadTIM for reconfiguring weblab infrastructures and the suggested XML schema for the log file | 101 |

| Figure 4.19: A thin implementation of the IEEE1451.0 Std. layered structure.                                                       | 102 |

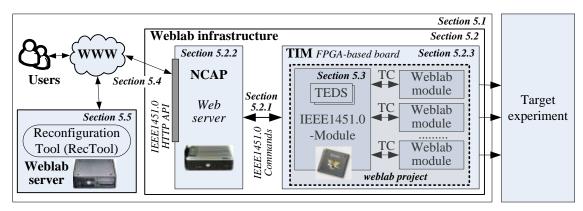

| Figure 5.1: Bock diagrams of the implemented weblab architecture                                                                   | 108 |

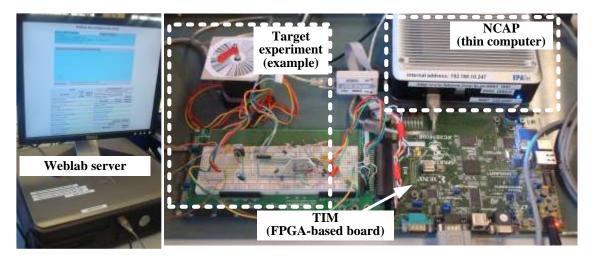

| Figure 5.2: Picture of the implemented weblab architecture.                                                                        | 108 |

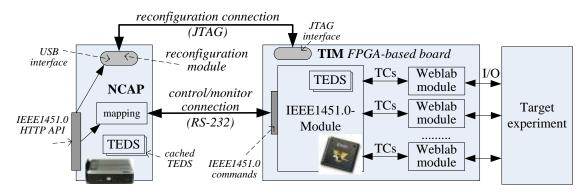

| Figure 5.3: Designed weblab infrastructure based on the IEEE1451.0 NCAP-TIM reference model.                                       | 109 |

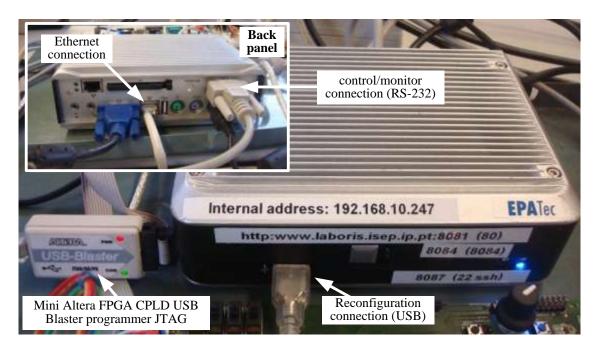

| Figure 5.4: Photograph of the NCAP implemented using a thin-client computer.                                                       | 111 |

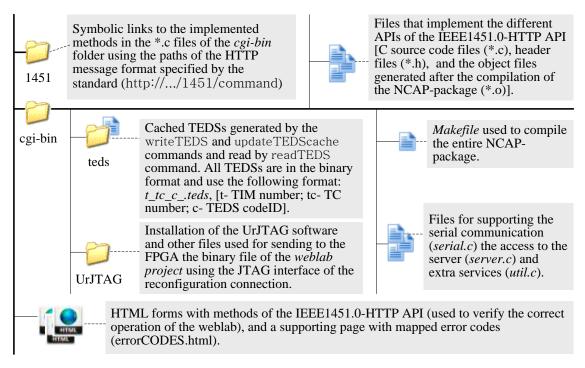

| Figure 5.5: NCAP-package folder organization.                                                                                      | 111 |

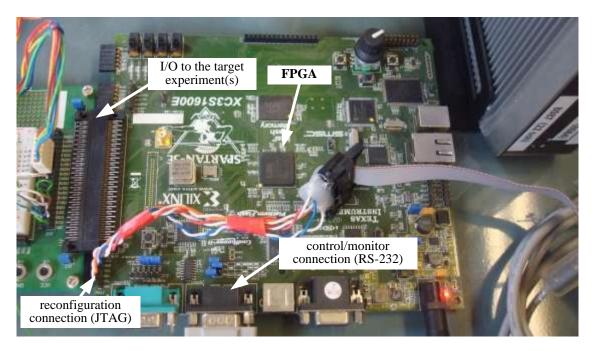

| Figure 5.6: Picture of the FPGA-based board where the TIM is implemented                                                           | 113 |

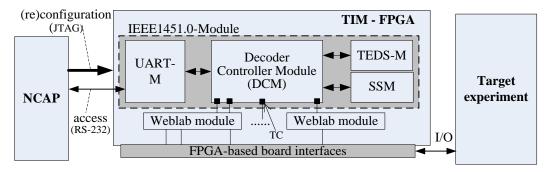

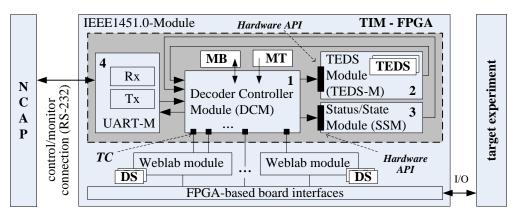

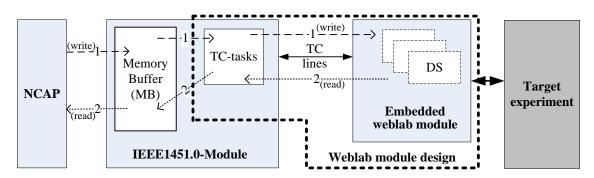

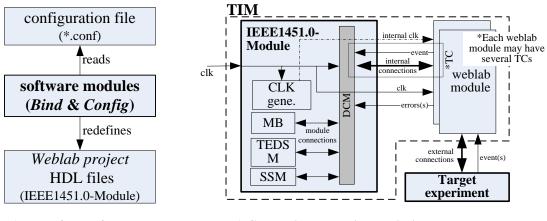

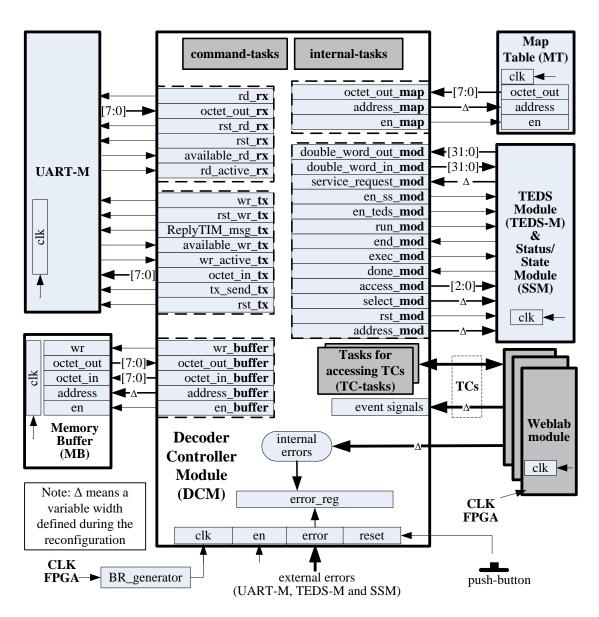

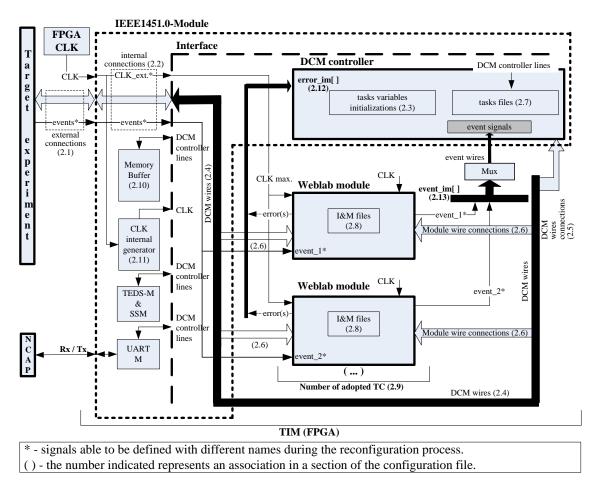

| Figure 5.7: Overview of the IEEE1451.0-compliant module (IEEE1451.0-Module)                                                        | 114 |

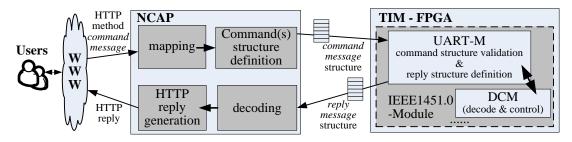

| Figure 5.8: NCAP-TIM accessing mechanism.                                                                                          | 115 |

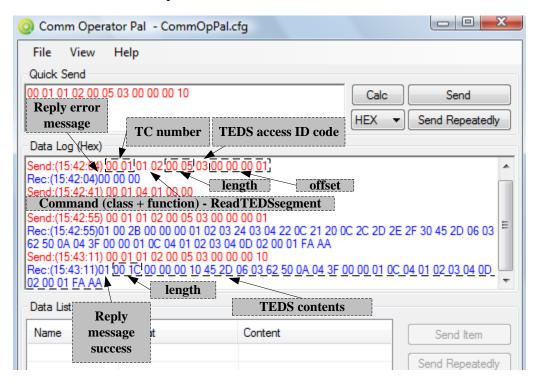

| Figure 5.9: Example of commands sent to the TIM reconfigured with an I/O weblab module using Comm Operator Pal serial port tool    |     |

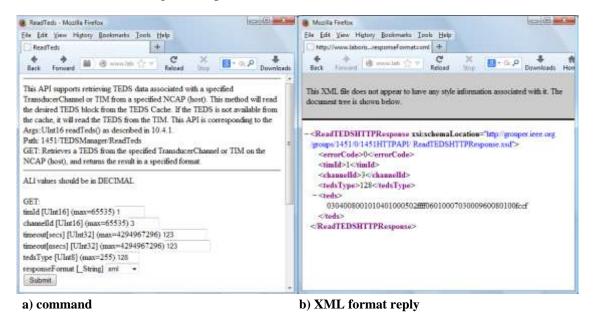

| Figure 5.10: Example of a ReadTEDS command and the associated reply in XML format issued us the IEEE1451.0-HTTP API.               | -   |

| Figure 5.11: Web interface of the weblab reconfiguration tool                                                                      | 119 |

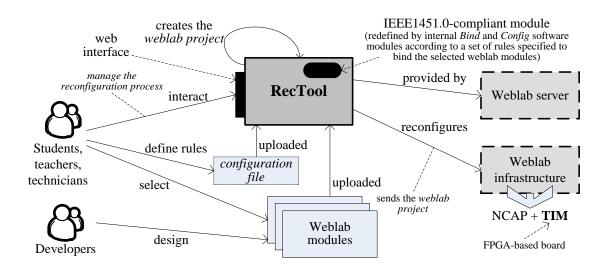

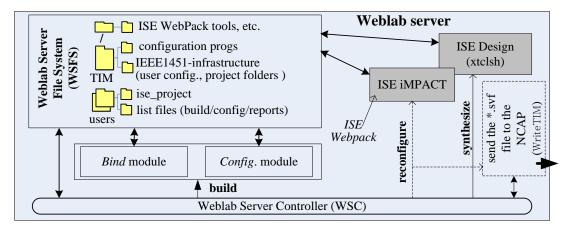

| Figure 6.1: Conceptual diagram with tools, resources and the human actors involved in the reconfiguration process.                 | 125 |

| Figure 6.2: Internal modules of the IEEE1451.0-Module                                                                              | 127 |

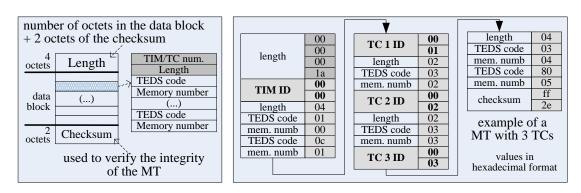

| Figure 6.3: MT structure and an example with 3 TCs.                                                                                | 130 |

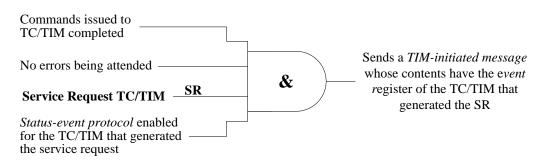

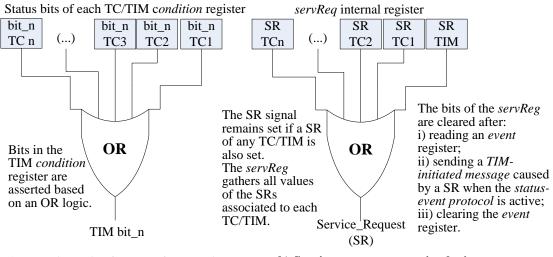

| Figure 6.4: Implemented logic for the status-event protocol                                                                        | 131 |

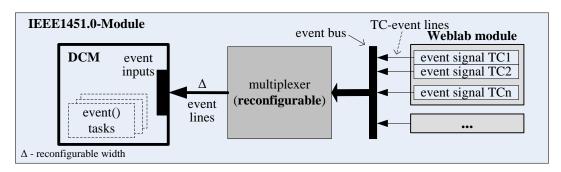

| Figure 6.5: Adopted architecture to handle events generated by weblab modules                                                      | 132 |

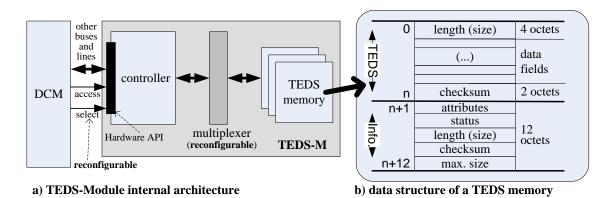

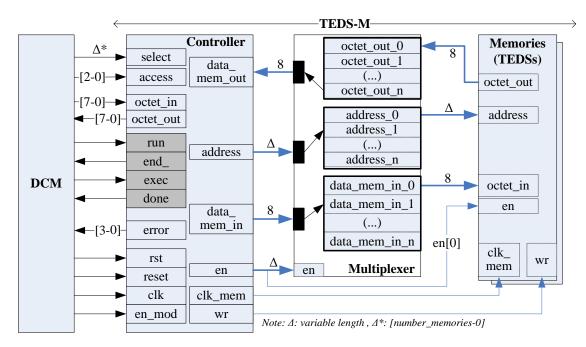

| Figure 6.6: The TEDS-M architecture and the data structure of a TEDS.                                                              | 133 |

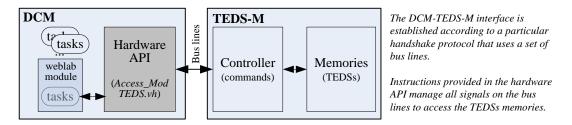

| Figure 6.7: Layered structure supported by the <i>Access_ModTEDS</i> hardware API to access the TE memories reconfigured in the TEDS-M. |          |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------|

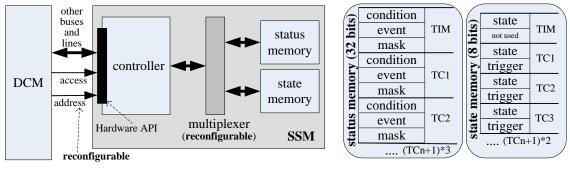

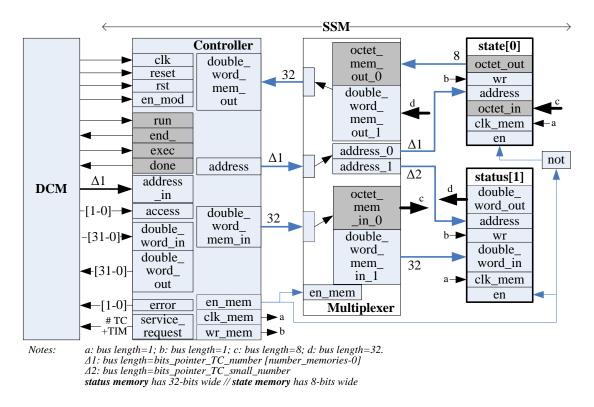

| Figure 6.8: The SSM architecture and the status/state memories structures                                                               | 135      |

| Figure 6.9: Implemented logic for the <i>condition registers</i> and for the SR signal                                                  | 137      |

| Figure 6.10: Layered structure supported by the <i>Access_ModStatusState</i> hardware API to access SSM status and the state memories.  |          |

| Figure 6.11: The architecture of the UART-M and the interface with the remaining modules of the IEEE1451.0-Module.                      |          |

| Figure 6.12: Parts required for defining a weblab module compatible with the IEEE1451.0-Modu                                            | ıle 139  |

| Figure 6.13: Data flow between the DCM and the weblab modules                                                                           | 140      |

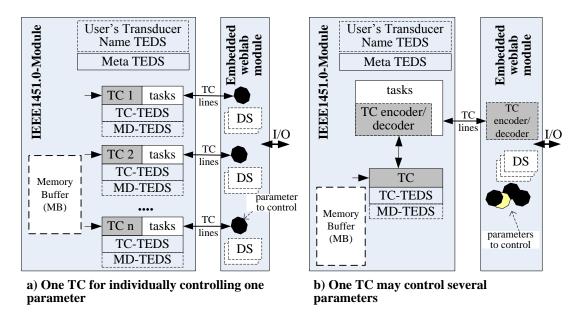

| Figure 6.14: Possibilities for controlling weblab modules parameters using TCs.                                                         | 141      |

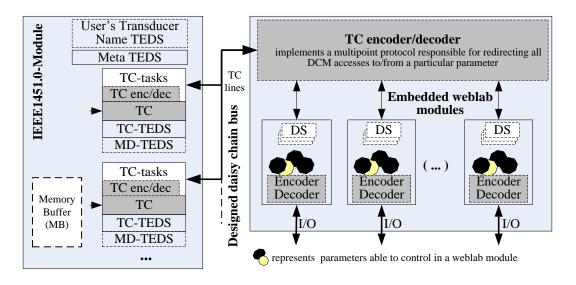

| Figure 6.15: Control of a daisy chain bus with the modules connected to the IEEE1451.0-Module                                           | e142     |

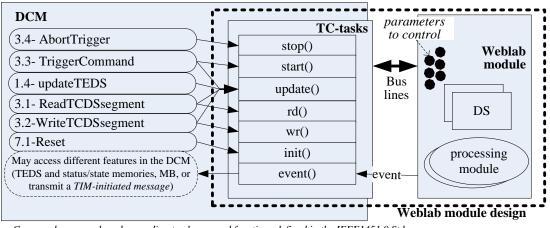

| Figure 6.16: Association between IEEE1451.0 commands and TC-tasks                                                                       | 143      |

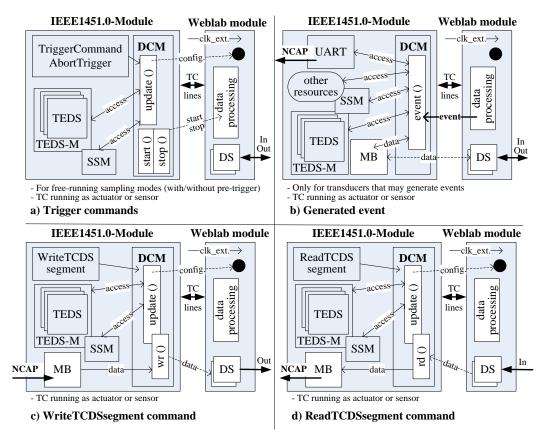

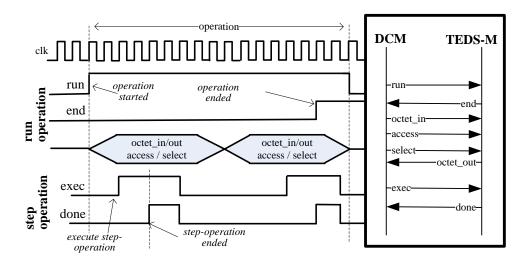

| Figure 6.17: Operational sequences performed by the TC-tasks.                                                                           | 145      |

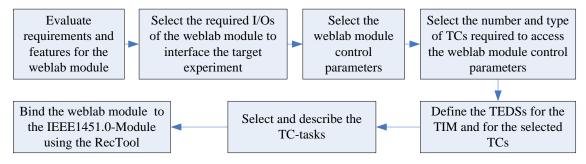

| Figure 6.18: Methodology for designing weblab modules compatible with the IEEE1451.0-Modu                                               | ıle 146  |

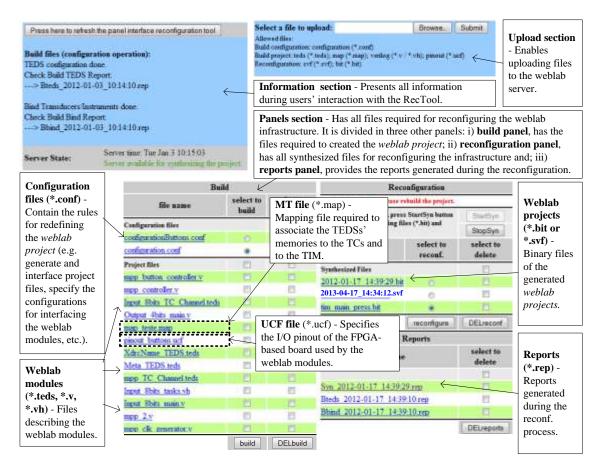

| Figure 6.19: The RecTool interface panels and files used for reconfiguring the weblab infrastruct                                       | ure. 147 |

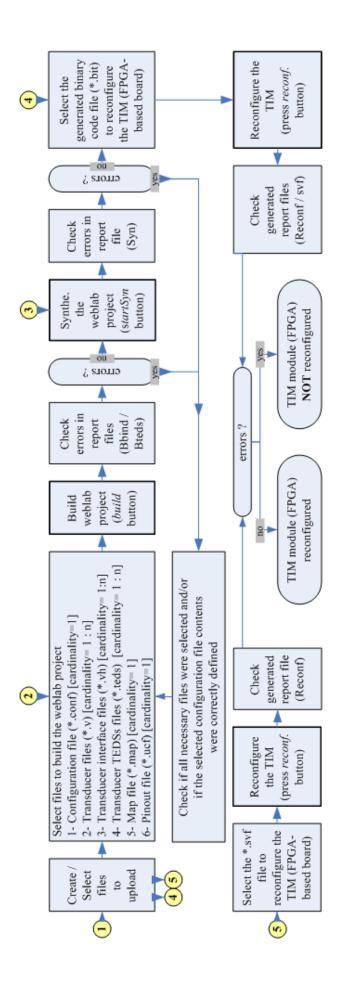

| Figure 6.20: The complete reconfiguration sequence using the RecTool.                                                                   | 149      |

| Figure 6.21: Role of the software modules running in the RecTool and connections established w the TIM                                  |          |

| Figure 6.22: Weblab server internal modules and the actions used for creating the <i>weblab project</i> reconfigures the TIM.           |          |

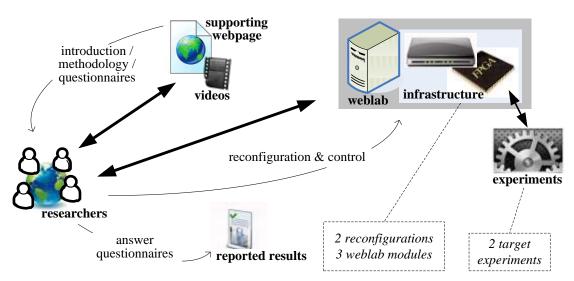

| Figure 7.1: Scenario adopted to validate and verify the implemented weblab.                                                             | 160      |

| Figure 7.2: Involved researchers in the validation & verification process.                                                              | 161      |

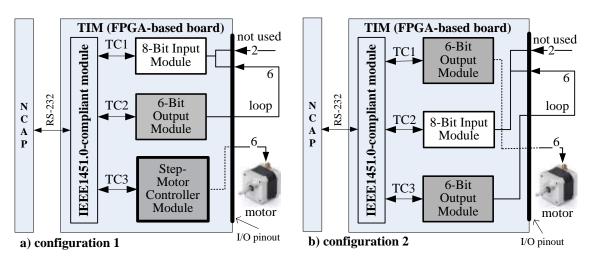

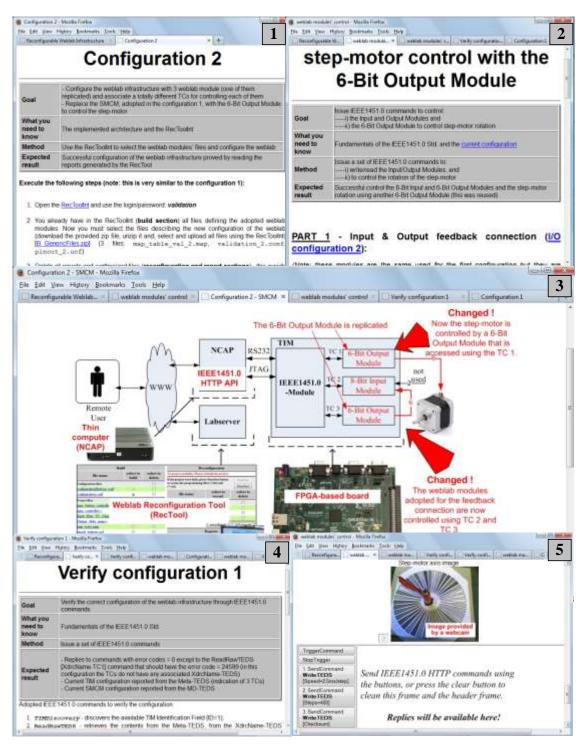

| Figure 7.3: Configurations defined to the weblab infrastructure.                                                                        | 162      |

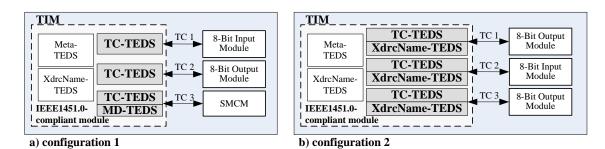

| Figure 7.4: Adopted TEDSs in each configuration.                                                                                        | 163      |

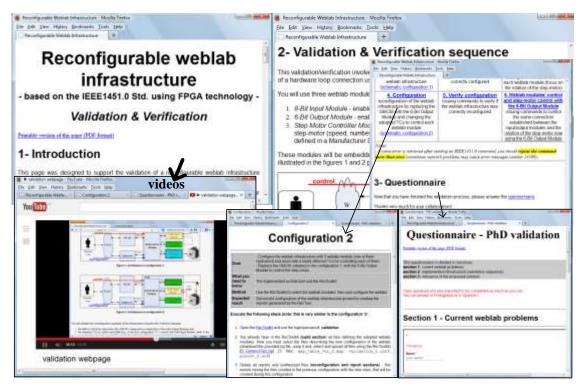

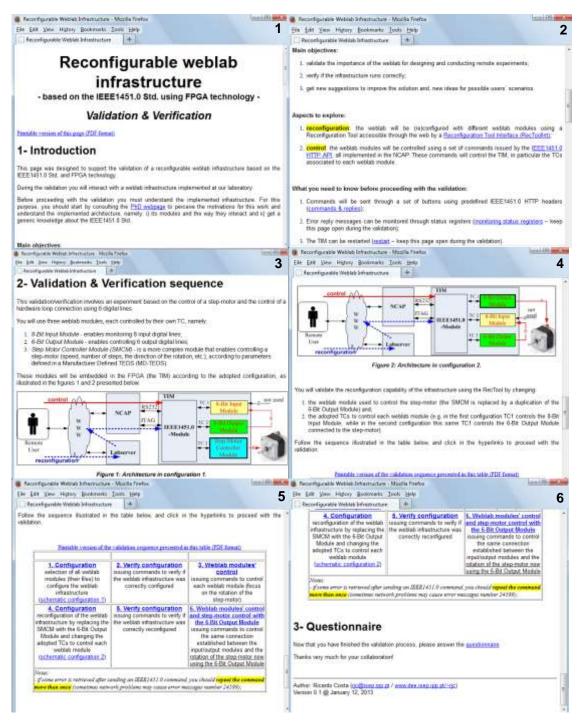

| Figure 7.5: Screenshots of the supporting webpage and videos provided to guide researchers duri validation & verification process.      | -        |

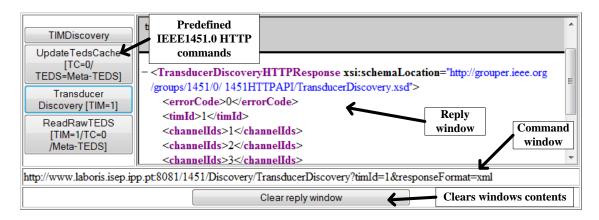

| Figure 7.6: Typical interface adopted for issuing IEEE1451.0 commands using the IEEE1451.0-I<br>API.                                    |          |

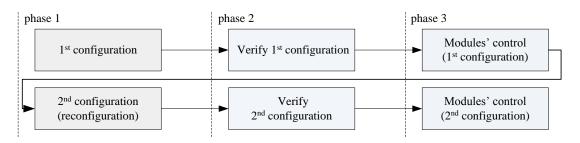

| Figure 7.7: Phases adopted for the researchers' interaction with the weblab.                                                            | 165      |

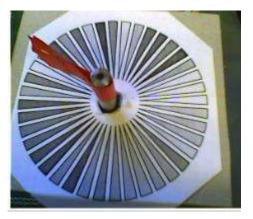

| Figure 7.8: Picture of the adopted step-motor and video frame of its axis provided by the support webpage                               | -        |

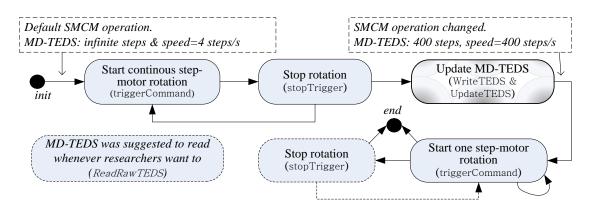

| Figure 7.9: Command sequence applied to control the step-motor rotation in the 1 <sup>st</sup> configuration                            | ı 167    |

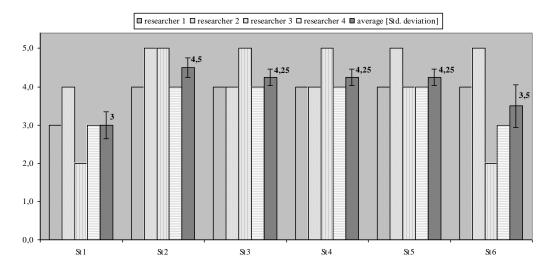

| Figure 7.10: Graph results with the accordance with six problems currently faced by weblabs                                             | 169      |

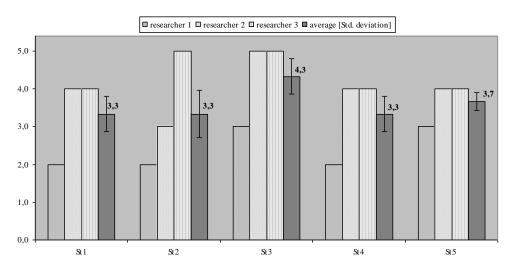

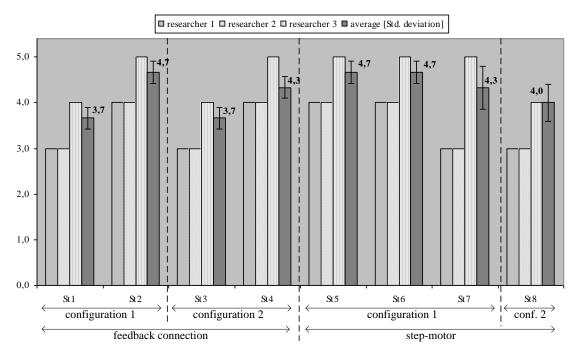

| Figure 7.11: Graph results with the accordance with the configuration phases                                                            | 171      |

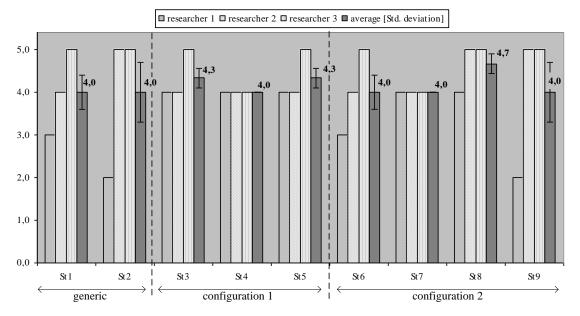

| Figure 7.12: Graph results with the accordance with the verify configuration phases                                                     | 172      |

| Figure 7.13: Graph results with the accordance with the weblab modules' control                                                         | 174      |

| Figure 7.14: Graph results with the accordance with the proposed weblab                                                                 | 175      |

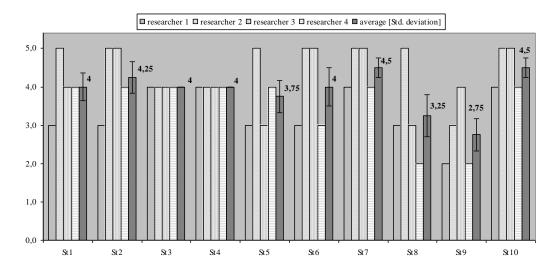

| Figure 8.1: Suggested sequence for the engineering practical work in distance learning.                                                                      | . 181 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 8.2: Screenshots of a tool being developed to facilitate the design of TEDSs, map and configuration files adopted during the reconfiguration process. | . 186 |

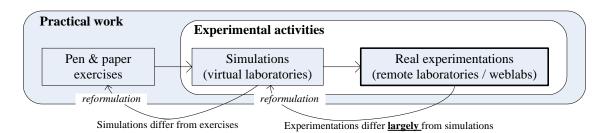

| Figure A.1: Structural elements of an FPGA.                                                                                                                  | . 205 |

| Figure B.1: Example of an FPGA-based board from Xilinx (Spartan 3E)                                                                                          | . 207 |

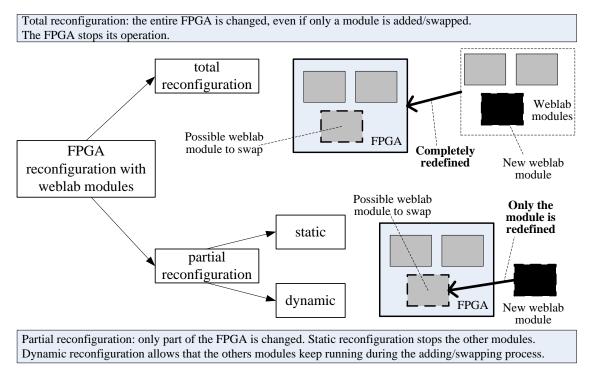

| Figure C.1: Possibilities for reconfiguring an FPGA with different weblab modules                                                                            | . 209 |

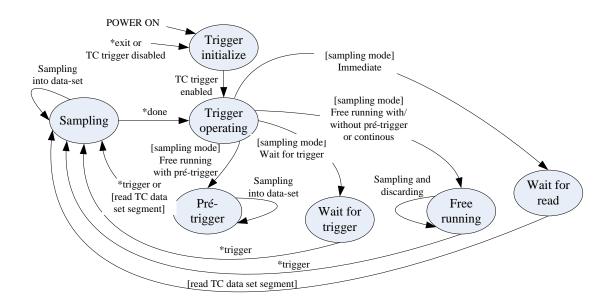

| Figure E.1: Sensor trigger states                                                                                                                            | . 215 |

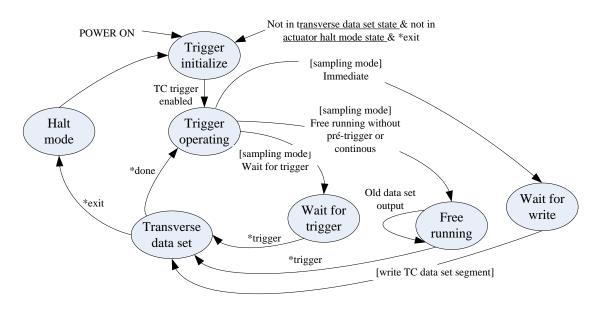

| Figure E.2: Actuator trigger states                                                                                                                          | . 215 |

| Figure E.3: Information notes for the trigger state diagrams                                                                                                 | .216  |

| Figure J.1: DCM schematics with all adopted buses for interfacing the other modules                                                                          | . 240 |

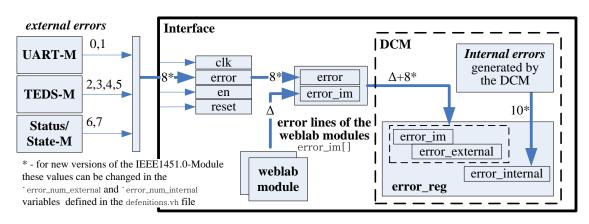

| Figure J.2: Illustration of the adopted registers to handle errors                                                                                           | 243   |

| Figure J.3: TEDS-M internal schematics.                                                                                                                      | . 245 |

| Figure J.4: Handshake protocol adopted for the DCM-TEDS-M interface                                                                                          | 246   |

| Figure J.5: SSM internal schematics                                                                                                                          | . 249 |

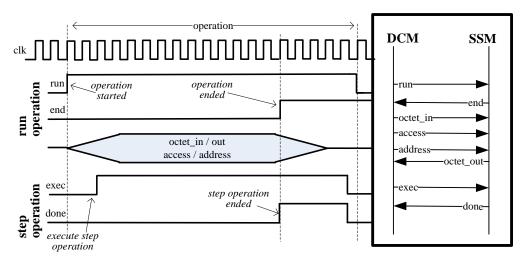

| Figure J.6: Handshake protocol for the DCM-SSM interface.                                                                                                    | . 250 |

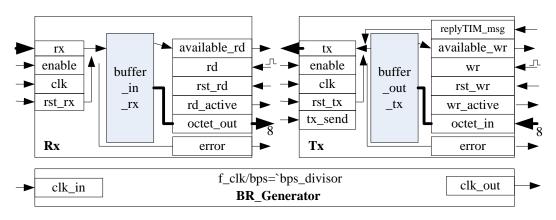

| Figure J.7: Modules of the UART-M and its buses and lines                                                                                                    | . 252 |

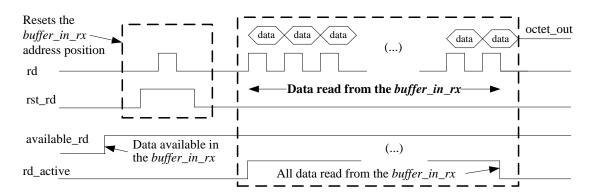

| Figure J.8: Handshake protocol used to read data from the <i>Rx</i> module                                                                                   | . 253 |

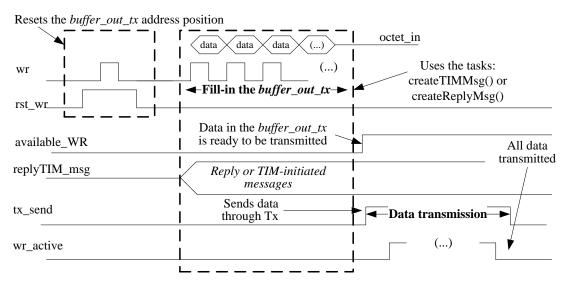

| Figure J.9: Handshake protocol used to fill-in the <i>buffer_out_tx</i> and to transmit data to the NCAP                                                     | . 254 |

| Figure K.1: Freeware hexadecimal editor XVI32 used to define TEDSs and MTs.                                                                                  | . 256 |

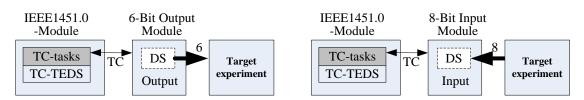

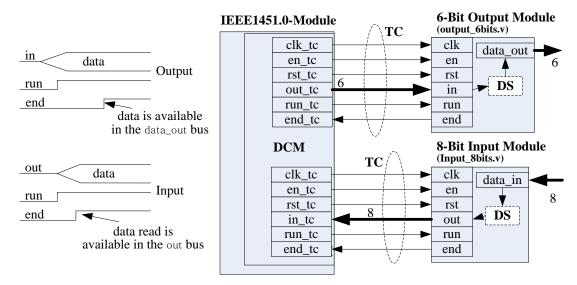

| Figure K.2: Digital I/Os weblab modules connected to the IEEE1451.0-Module                                                                                   | . 257 |

| Figure K.3: Buses, lines and the handshake protocol of the I/O weblab modules.                                                                               | . 257 |

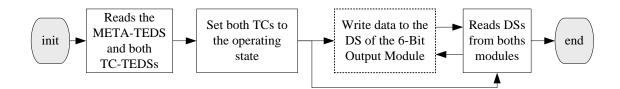

| Figure K.4: Sequence of commands issued to the I/O digital weblab modules                                                                                    | . 259 |

| Figure K.5: Commands issued to validate the I/O digital weblab modules                                                                                       | . 259 |

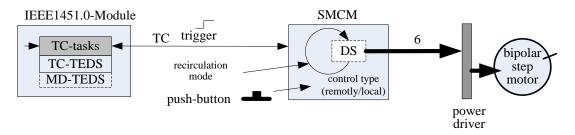

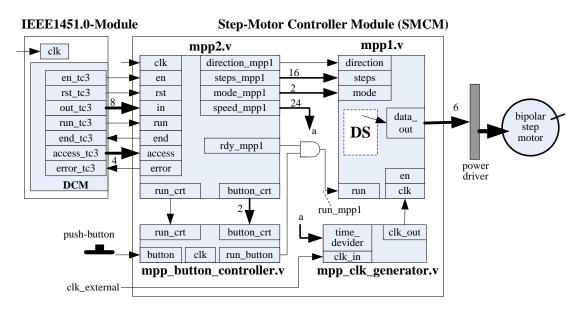

| Figure K.6: SMCM connected to the IEEE1451.0-Module.                                                                                                         | . 260 |

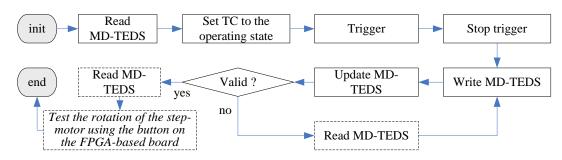

| Figure K.7: Handshake protocol used to access the SMCM through the TC-tasks.                                                                                 | . 262 |

| Figure K.8: The SCMC HDL modules and buses.                                                                                                                  | . 263 |

| Figure K.9: Sequence of commands adopted for validating the SMCM                                                                                             | . 264 |

| Figure K.10: IEEE1451.0 commands issued to validate the SMCM                                                                                                 | . 265 |

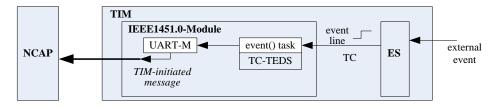

| Figure K.11: Event Sensor connected to the IEEE1451.0-Module                                                                                                 | . 265 |

| Figure K.12: <i>TIM-initiated message</i> retrieved from the ES after detecting an event                                                                     | . 266 |

| Figure L.1: Reconfiguration schematics.                                                                                                                      | . 274 |

| Figure M.1: Screenshots of the supporting webpage front panels                                                                                               | . 283 |

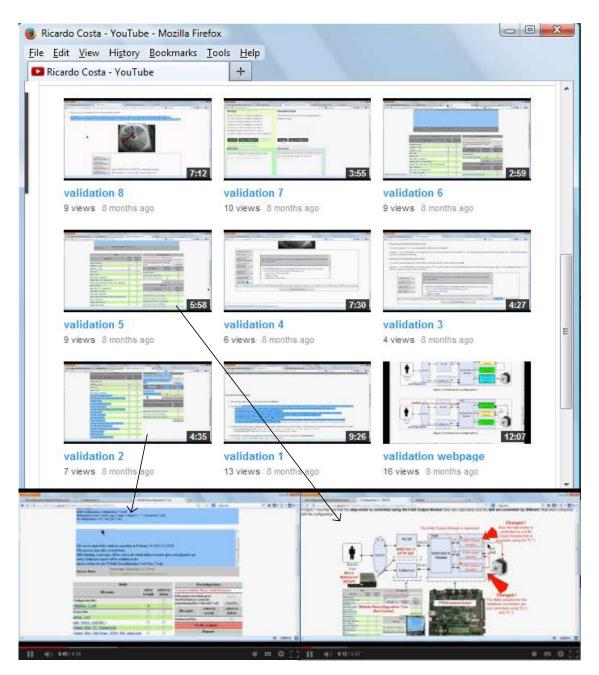

| Figure M.2: Videos exemplifying the interaction with the weblab                                                                                              | . 284 |

| Figure M.3: Table grid provided in the supporting webpage with the different stages of the adopted methodology in the validation and reconfiguration process | 289   |

| Figure M.4: Examples of webpages used during the validation and verification process.                                                                        | . 290 |

# **Tables**

| Table 2.1: Some concepts associated to E-learning.                                                                                                                              | 12  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2: A personal comparison among laboratory types.                                                                                                                        | 17  |

| Table 2.3: Human actors in Remote Experimentation.                                                                                                                              | 22  |

| Table 2.4: Non-human actors in Remote Experimentation.                                                                                                                          | 22  |

| Table 2.5: Associations among human actors in the RE actor-network                                                                                                              | 23  |

| Table 2.6: Associations among technical actors in the RE actor-network.                                                                                                         | 24  |

| Table 2.7: Associations between technical and human actors in the RE actor-network                                                                                              | 25  |

| Table 2.8: Experimental learning goals with weblabs.                                                                                                                            | 27  |

| Table 2.9: Weblabs' repositories, projects and consortiums.                                                                                                                     | 40  |

| Table 3.1: Overview of some well known instrumentation bus standards.                                                                                                           | 47  |

| Table 3.2: The IEEE1451.x Std. family.                                                                                                                                          | 58  |

| Table 3.3: A selection of commercial MWS.                                                                                                                                       | 67  |

| Table 3.4: A selection of TCP/IP cores.                                                                                                                                         | 68  |

| Table 3.5: Considerations about the number of FPGAs versus the weblab modules required for         implementing a reconfigurable infrastructure based on an hybrid architecture | 69  |

| Table 4.1: IEEE1451.0 main TC sampling modes and complemented modes.                                                                                                            | 83  |

| Table 4.2: IEEE1451.0 TIM to NCAP transmission modes.                                                                                                                           | 84  |

| Table 4.3: Classes of standard commands                                                                                                                                         | 87  |

| Table 4.4: IEEE1451.0 Std. HTTP API (paths and methods).                                                                                                                        |     |

| Table 4.5: LabTEDS fields.                                                                                                                                                      | 96  |

| Table 4.6: Mapping of HTTP APIs' methods to TIM commands.                                                                                                                       | 102 |

| Table 6.1: Implemented commands to access the TEDS-M                                                                                                                            | 133 |

| Table 6.2: Memory selection in the TEDS-M.                                                                                                                                      | 133 |

| Table 6.3: Instructions provided by the Access_ModTEDS hardware API.                                                                                                            | 134 |

| Table 6.4: Implemented commands to access the SSM.                                                                                                                              | 136 |

| Table 6.5: Instructions provided by the Access_ModStatusState hardware API                                                                                                      | 137 |

| Table 7.1: Accordance with six problems currently faced by weblabs.                                                                                                             | 169 |

| Table 7.2: Accordance with the configuration phases.                                                                                                                            | 171 |

| Table 7.3: Accordance with the verify configuration phases.                                                                                                                     | 172 |

| Table 7.4: Accordance with the weblab modules' control.                                                                                                                         | 173 |

| Table 7.5: Accordance with the proposed weblab.                                                                                                                                 | 175 |

| Table C.1: Options for reconfiguring FPGAs.                                                                                                                                     | 210 |

| Table D.1: Meta-TEDS structure                                                                                                                                                  | 211 |

| Table D.2: TC-TEDS structure                                                                                                       | 212 |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table D.3: TEDS' attributes implemented in an octet.                                                                               | 213 |

| Table D.4: TEDS' status implemented in an octet                                                                                    | 213 |

| Table F.1: Status bits defined by the IEEE1451.0 Std                                                                               | 217 |

| Table G.1: NCAPRegister method.                                                                                                    | 219 |

| Table G.2: NCAPDiscovery method.                                                                                                   | 220 |

| Table G.3: ReadLabTEDS method.                                                                                                     | 220 |

| Table G.4: WriteLabTEDS method.                                                                                                    | 221 |

| Table G.5: ReadTIM method.                                                                                                         | 221 |

| Table G.6: WriteTIM method.                                                                                                        | 222 |

| Table G.7: ReadLog method                                                                                                          | 222 |

| Table G.8: WriteLog method.                                                                                                        | 223 |

| Table H.1: Mapping the ReadData method to SamplingMode and ReadTCDSsegment commands                                                | 225 |

| Table H.2: Mapping the StartReadData and MeasurementUpdate methods to SamplingMode and       ReadTCDSsegment commands              | 226 |

| Table H.3: Mapping the WriteData method to SamplingMode and WriteTCDSsegment commands.                                             | 226 |

| Table H.4: Mapping the StartWriteData method to SamplingMode and WriteTCDSs commands                                               | 227 |

| Table H.5: Mapping the ReadTEDS and ReadRawTEDS methods to the ReadTEDSsegment command.                                            | 227 |

| Table H.6: Mapping the UpdateTEDSCache to the ReadTEDSsegment command.                                                             | 228 |

| Table H.7: Mapping the WriteTEDS and WriteRawTEDS methods to the WriteTEDSsegment command.                                         | 228 |

| Table H.8: Mapping the SendCommand method.                                                                                         | 229 |

| Table H.9: Mapping the StartCommand and CommandComplete methods                                                                    | 229 |

| Table H.10: Mapping the Trigger and the StartTrigger methods to commands ReadTEDSsegment,         SamplingMode and TriggerCommand. | 229 |

| Table I.1: Error source codes.                                                                                                     |     |

| Table I.2: Error enumeration codes.                                                                                                | 231 |

| Table J.1: List with the DCM internal registers                                                                                    | 233 |

| Table J.2: DCM internal-tasks                                                                                                      | 235 |

| Table J.3: Commands common to the TIM and to each TC (ClassID=1).                                                                  | 236 |

| Table J.4: Transducer operating state commands (ClassID=3).                                                                        |     |

| Table J.5: Transducer either idle or operating state commands (ClassID=4).                                                         |     |

| Table J.6: TIM any state commands (ClassID=7).                                                                                     |     |

| Table J.7: MB definition (pieces of code in *.conf and definitions_GENERIC.vh files).                                              |     |

| Table J.8: Buses and lines adopted for the DCM-MB interface.                                                                       | 241 |

| Table J.9: Sequence for accessing to the MB (Verilog code examples)                                                             | 241 |

|---------------------------------------------------------------------------------------------------------------------------------|-----|

| Table J.10: Buses and lines adopted for the DCM-MT interface                                                                    | 242 |

| Table J.11: Sequence for reading the MT (Verilog code example).                                                                 | 242 |

| Table J.12: Error codes mapped from the <i>condition register</i> to the error_reg                                              | 243 |

| Table J.13: Example of a <i>definitions_TEDS.vh</i> file automatically created during the reconfiguration process.              |     |

| Table J.14: Buses and lines adopted for the DCM-TEDS-M interface.                                                               | 245 |

| Table J.15: TEDS-M hardware API instructions (available in file: Access_ModTEDS.vh)                                             | 247 |

| Table J.16: Sequences for accessing the TEDS-M hardware API instructions                                                        | 248 |

| Table J.17: Example of a <i>definitions_GENERIC.vh</i> file automatically created during the reconfiguration process.           | 248 |

| Table J.18: Buses and lines adopted for the DCM-SSM interface                                                                   | 249 |

| Table J.19: SSM hardware API instructions (available in the file: <i>ModStatusState.vh</i> )                                    | 250 |

| Table J.20: Sequences for accessing the SSM hardware API instructions.                                                          | 251 |

| Table J.21: Signals used by the Rx module (data reception from the NCAP).                                                       | 252 |

| Table J.22: Signals used by the Tx module (data transmission to the NCAP).                                                      | 252 |

| Table K.1: Example of Verilog HDL code for implementing TC-tasks using the mandatory end_tc_task and attending_event variables. | 255 |

| Table K.2: TC-TEDS relevant fields defined to control the 8-Bit Input Module.                                                   | 257 |

| Table K.3: TC-TEDS relevant fields defined to control the 6-Bit Output Module                                                   | 258 |